Plus de 50 ans après sa première conjecture, Gordon Moore continue de diriger (indirectement) l’amélioration de la densité de transistors sur une puce de silicium. Mais sa célèbre « Loi » va droit dans le mur, et le crash est prévu pour 2021.

Credit : Erik Vrielink

Credit : Erik Vrielink

| A lire aussi : – Miniaturisation des transistors et agrandissement des wafers : comprendre les enjeux technologiques |

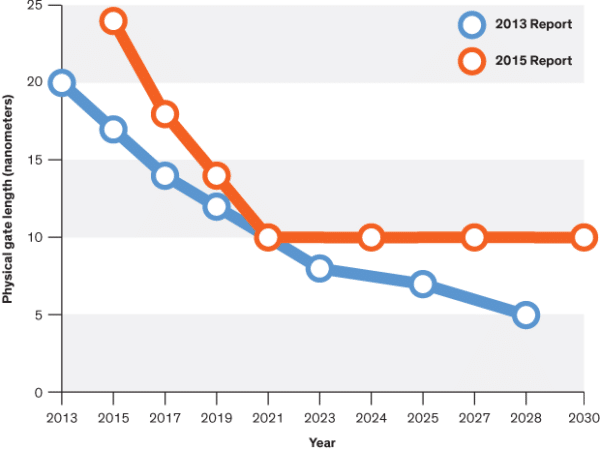

Tous les deux ans, la Semiconductor Industry Association (SIA) qui représente les principaux fabricants de semi-conducteurs américains, publie une feuille de route extrêmement complète (elle couvre les composants, CPU, mémoires flash et DRAM, mais également les gros systèmes, datacenters et autres produits IoT) pour les prochaines décennies. Cette année, l’International Technology Roadmap for Semiconductors (ITRS) – rebaptisé « ITRS 2.0 » pour l’occasion – fixe les grandes lignes pour les 15 prochaines années, avec d’importants changements par rapport au précédent rapport de 2013, en particulier la fin annoncée et datée de la « Loi » de Moore.

La limite des 10 nm

Alors que l’industrie des semi-conducteurs s’est fixé depuis des décennies comme objectif de suivre la célèbre Loi de Moore, à savoir doubler tous les deux ans le nombre de transistors sur une surface donnée, la limite physique de la réduction de la finesse de gravure nécessaire pour continuer à miniaturiser ces transistors approche à grand pas.

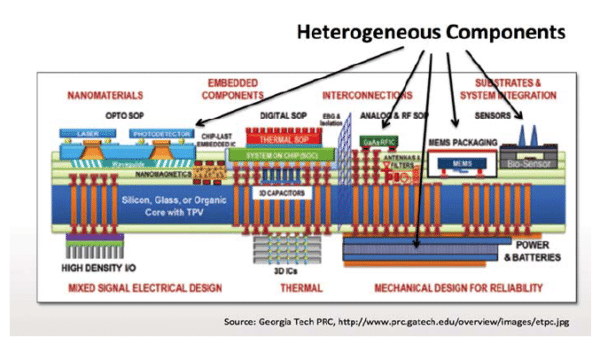

Alors que le rapport de 2013 estimait que la longueur de la grille d’un transistor – et non pas la finesse de gravure, même si ces deux valeurs sont liées – continuerait à diminuer jusqu’à 5 nm en 2028, la SIA prédit désormais que cette même mesure atteindra un plancher de 10 nm dès 2021. C’en sera alors terminé de la diminution de la taille physique de la grille des transistors. Mais les industriels travaillent déjà sur l’après-2021 : VGAA (Vertical gate-all-around), LGAA (Lateral gate-all-around)… Il faudra désormais « penser » en 3D pour améliorer l’intégration de composants hétérogènes !