Les puces sont nos amies

« Mais au fait, comment fabrique-t-on un processeur ? ». C’est à cette question que nous avons voulu répondre le plus simplement possible. Nous avions contacté Intel en 2009 pour avoir un résumé de toutes les étapes de fabrication d’un processeur. Aujourd’hui, nous mettons à jour ce diapo explicatif avec la méthode de gravure en 22nm High-K Metal Gate à transistors 3D, au goût du jour, avec de nouvelles images et une vidéo. En 2018, seule la finesse de gravure a diminué en 14 nm, mais le procédé reste identique. Reportage sur les étapes essentielles de la fabrication du produit manufacturé le plus complexe au monde.

Votre processeur est né des sables

Tout commence par le sable, composé à 25 % de silicium, l’élément chimique le plus répandu dans la croute terrestre après l’oxygène. Le sable, et plus particulièrement le quartz, contient un fort taux de silice sous forme de dioxyde de silicium (SiO2) qui se trouve être l’ingrédient de base pour fabriquer des semi-conducteurs. Cette matière première a donc le mérite d’être naturellement abondante.

Purification et culture

Après avoir séparé le silicium du sable brut, celui-ci est purifié à de nombreuses reprises pour arriver au standard de fabrication des semi-conducteurs, l’EGS (Electronic Grade Silicon). La pureté est telle que l’EGS peut ne contenir qu’un atome étranger par milliard d’atomes de silicium. A l’issue de ce traitement, le silicium est liquéfié à très haute température (plus de 1700 °C). On voit ici la création d’un cristal grâce au silicium liquide purifié : ce monocristal est qualifié de lingot.

Un gros lingot

Le lingot obtenu à partir de l’EGS est un monstre … de finesse : environ 100 Kilos, pureté du silicium de l’ordre de 99,9999 %.

Découpage du lingot

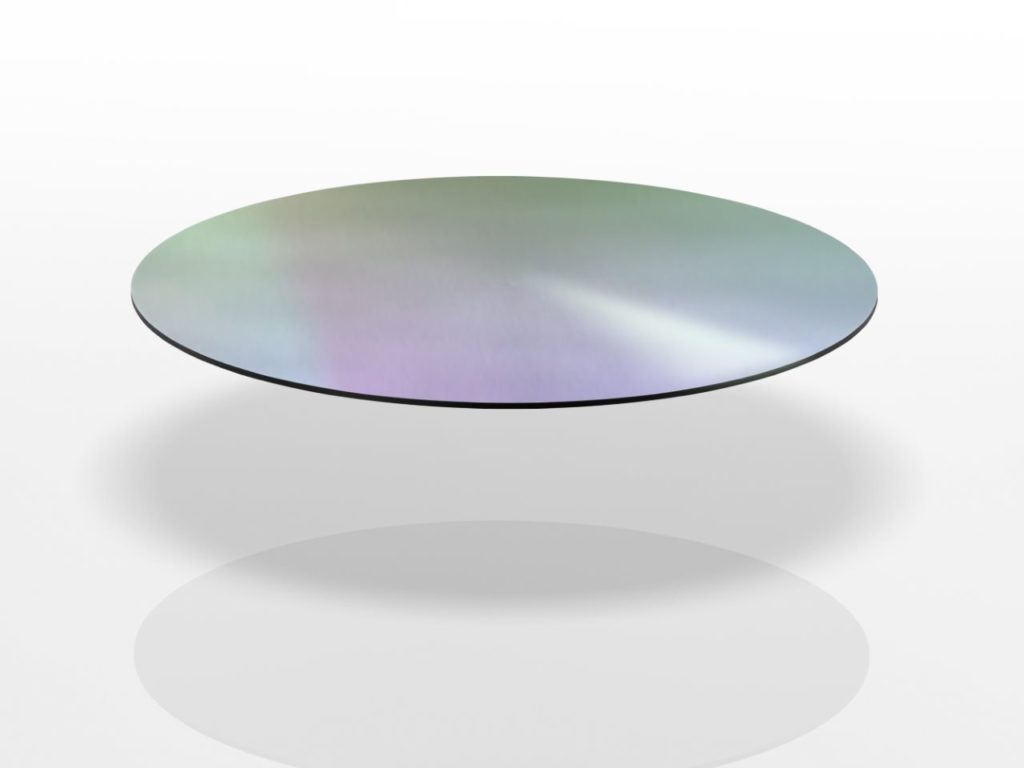

La phase suivante consiste à débiter le lingot en disques fins, que nous connaissons mieux sous le nom de wafers. Certains lingots dépassent 1,50 mètre et leur diamètre varie en fonction des wafers désirés : la plupart des processeurs actuels sont issus de wafers de 300 mm.

Polissage du wafer

Une fois coupés, les wafers sont polis jusqu’à l’obtention d’une finition miroir sans la moindre aspérité. Intel ne produit pas lui-même ses lingots et wafers, préférant se fournir auprès de partenaires en wafers prêts à être traités. Le procédé de fabrication High-K/Metal Gate utilise des wafers de 300 mm, tandis qu’à l’époque des premiers processeurs du géant de Santa Clara, ce dernier travaillait sur des wafers de 50 mm. La progression dans la taille des wafers permet ainsi de diminuer le coût unitaire des processeurs.

Traitement photorésistant

Le liquide bleu ci-dessus est un traitement photorésistant similaire à ceux utilisés pour les pellicules en photographie argentique. Un mouvement circulaire est imprimé aux wafers lors de cette étape afin d’optimiser la répartition du revêtement, doux et extrêmement fin.

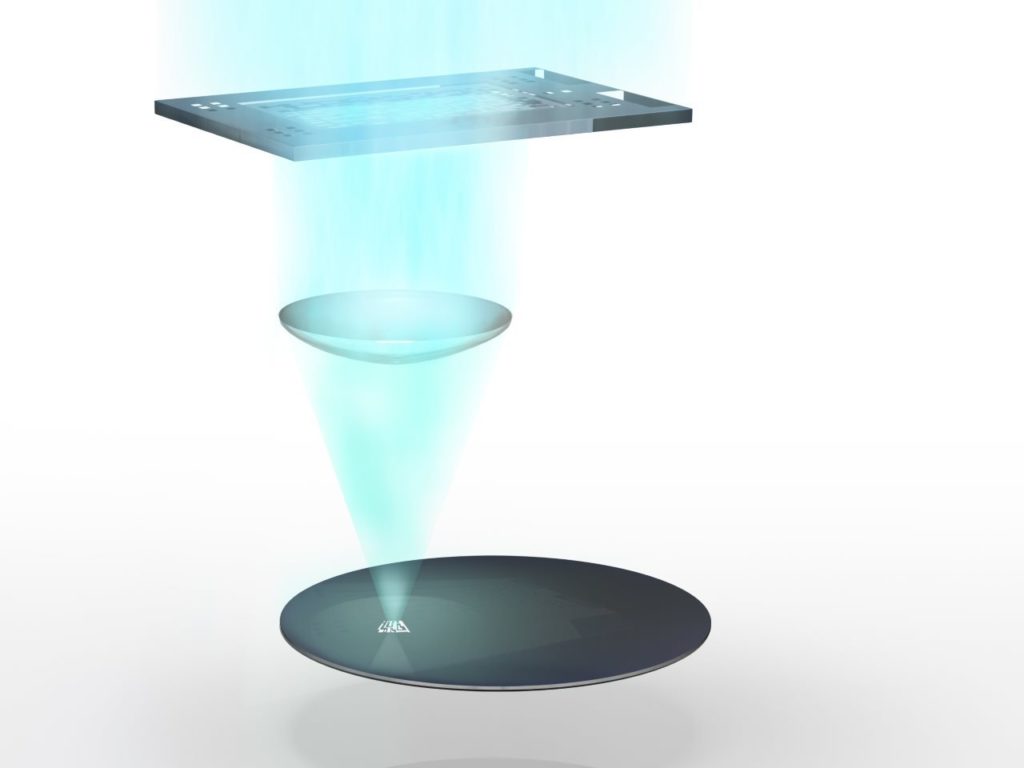

Exposition au rayonnement ultraviolet

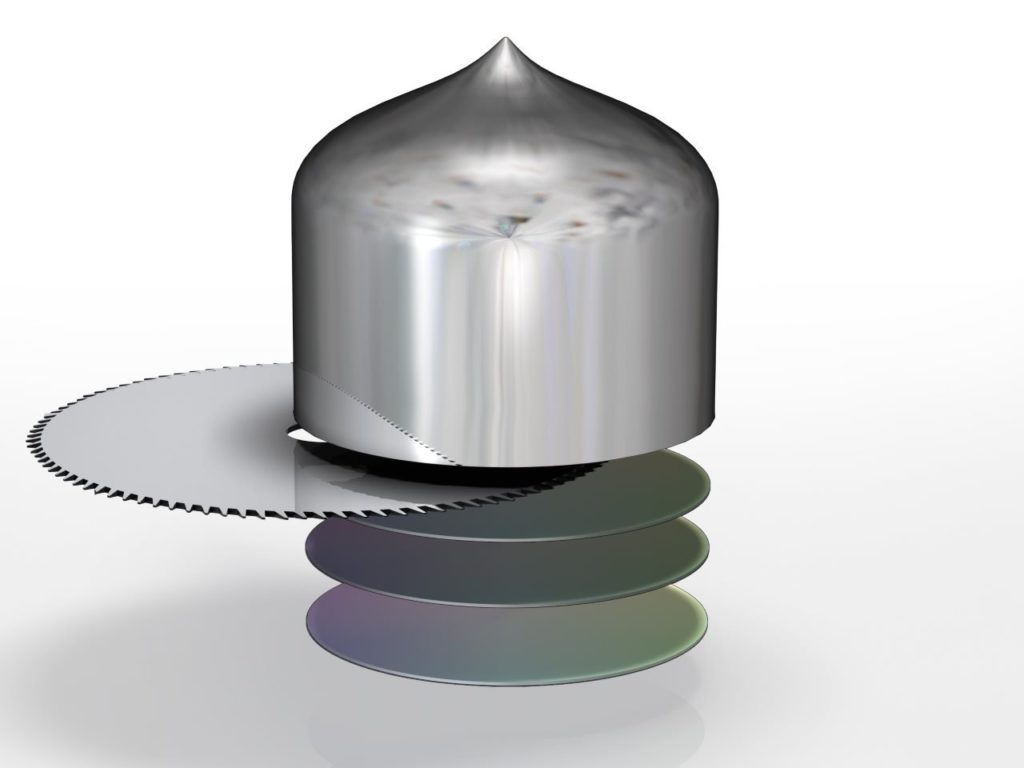

Le traitement photorésistant est ensuite exposé à la lumière ultraviolette (UV), voire ultraviolette extrême (EUV) avec les procédés de gravure les plus récents. Pour reprendre la comparaison avec l’argentique, la réaction chimique provoquée par les UV est semblable au changement d’état d’une pellicule lorsque l’on déclenche un appareil photo.

Les zones du wafer recouvertes du traitement photorésistant deviennent solubles après avoir été exposées aux UV. Cette exposition se fait à l’aide de masques qui agissent comme des pochoirs. La combinaison de ces masques et des UV permet de créer les divers motifs de circuits ; la création d’un processeur implique une répétition de ce procédé de manière à ce que de multiples couches se superposent. La lentille que l’on voit au centre des trois éléments réduit l’image du masque à un point focalisé. Ainsi, l’impression qui en résulte sur le wafer est une réduction linéaire du motif du maque.

Retrait des parties solubles

Les parties traitées aux UV sont ainsi rendues solubles, et retirées à l’aide d’un produit chimique, laissant les premières fondations de la puce.

Dopage aux ions

La galette est ensuite bombardé par un rayonnement d’ions qui vont doper le silicium qui n’est pas protégé par la couche photorésistante, altérant ses propriétés conductrices. Le silicium devient alors isolant ou conducteur, en fonction des ions qui le bombarde. C’est dans ces zones que les transistors seront formés. Le traitement photorésistant est ensuite totalement retiré par un procédé chimique.

Formation du transistor

Le transistor se forme donc dans une de ces zones bombardés d’ions, mesurant entre 50 et 200 nm. Une galette de silicium en regroupe des centaines de milliards aujourd’hui.

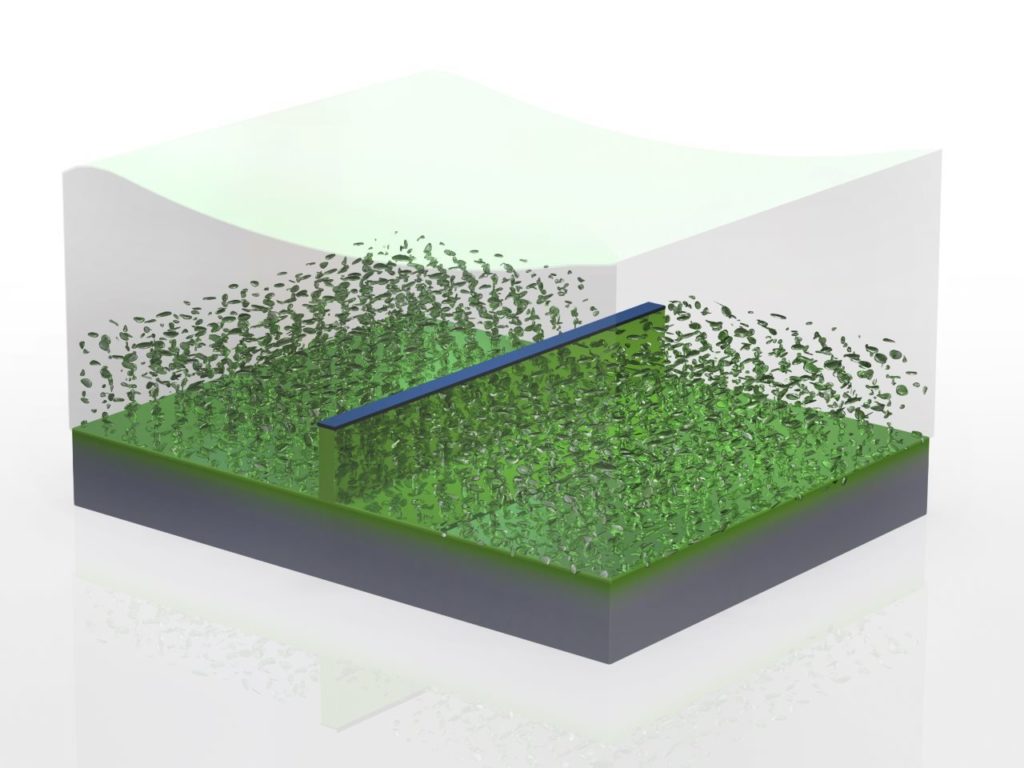

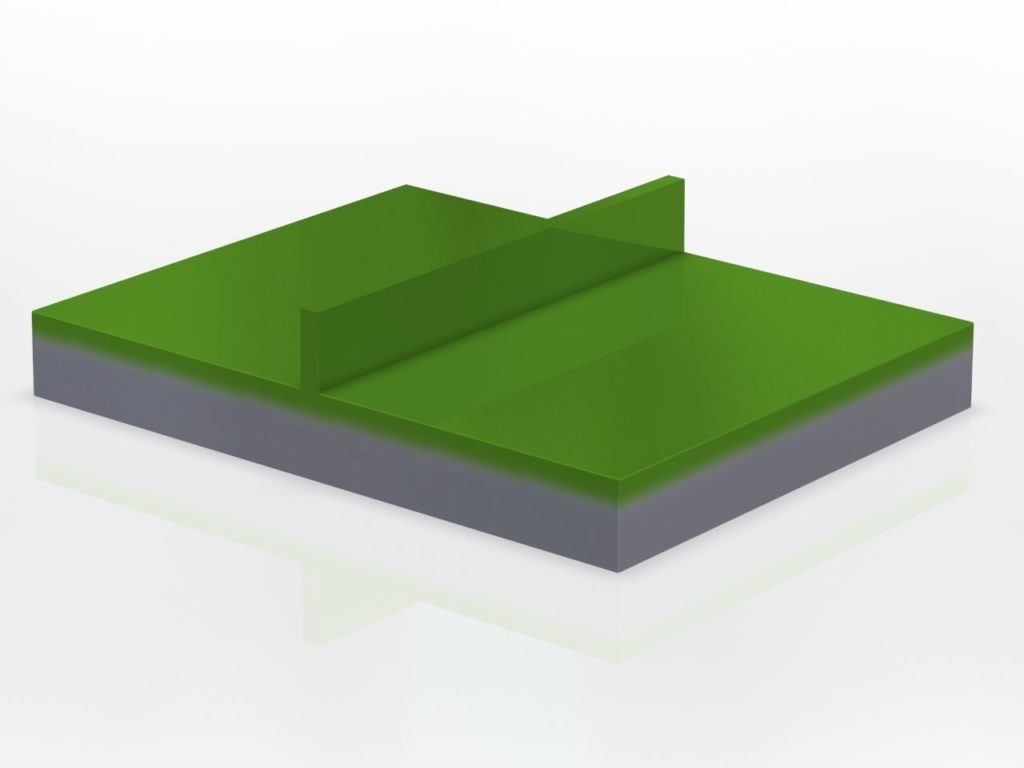

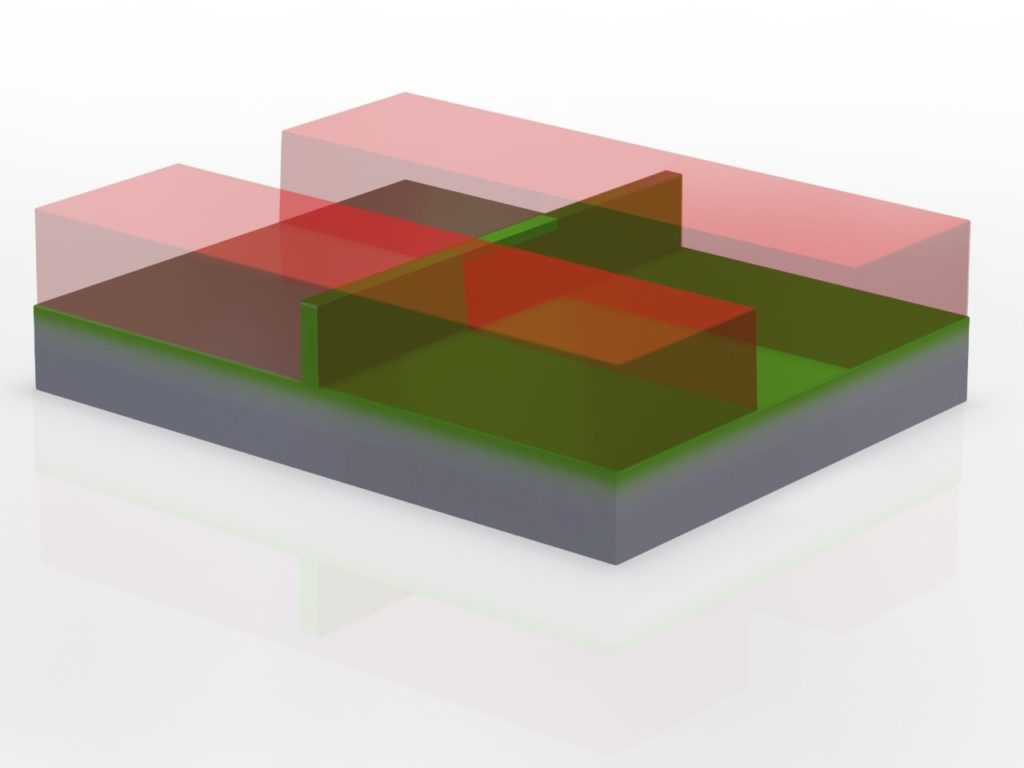

Gravure en profondeur

Ici, plusieurs agents chimiques gravent le wafer en profondeur autour des zones qui n’ont pas été traitées pour être photorésistantes par un masque, ici en bleu.

Retrait du revêtement photorésistant

Après la gravure en profondeur, le revêtement photorésistant est retiré. Ainsi, les formes prévues deviennent visibles.

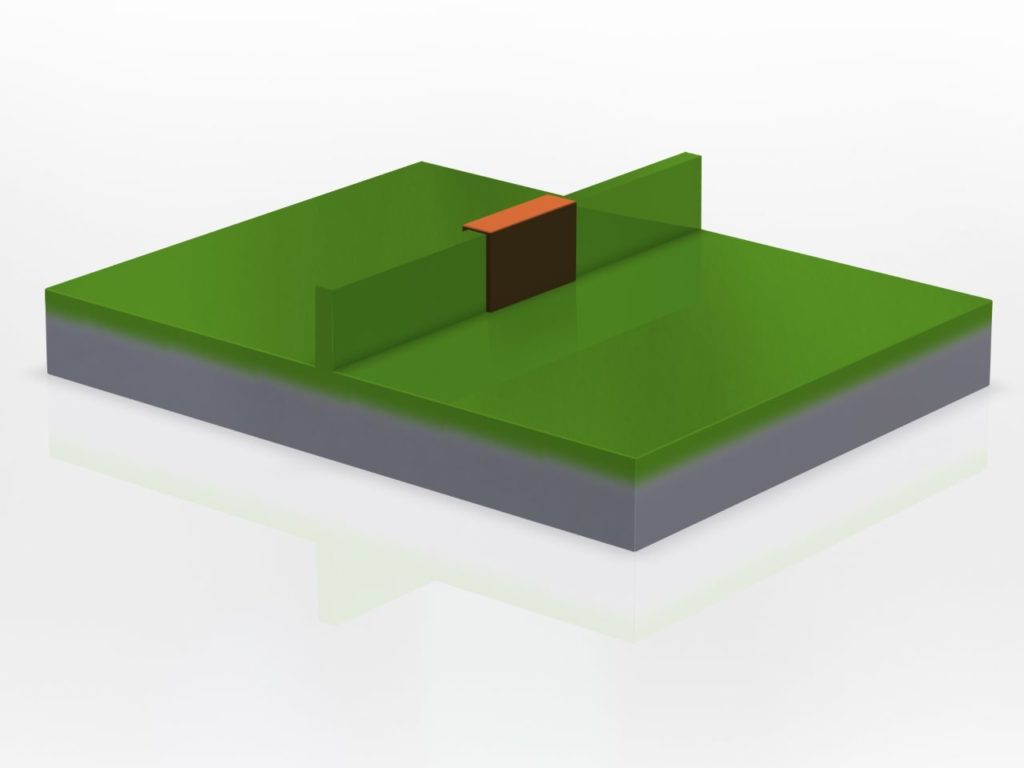

Nouveau traitement photorésistant

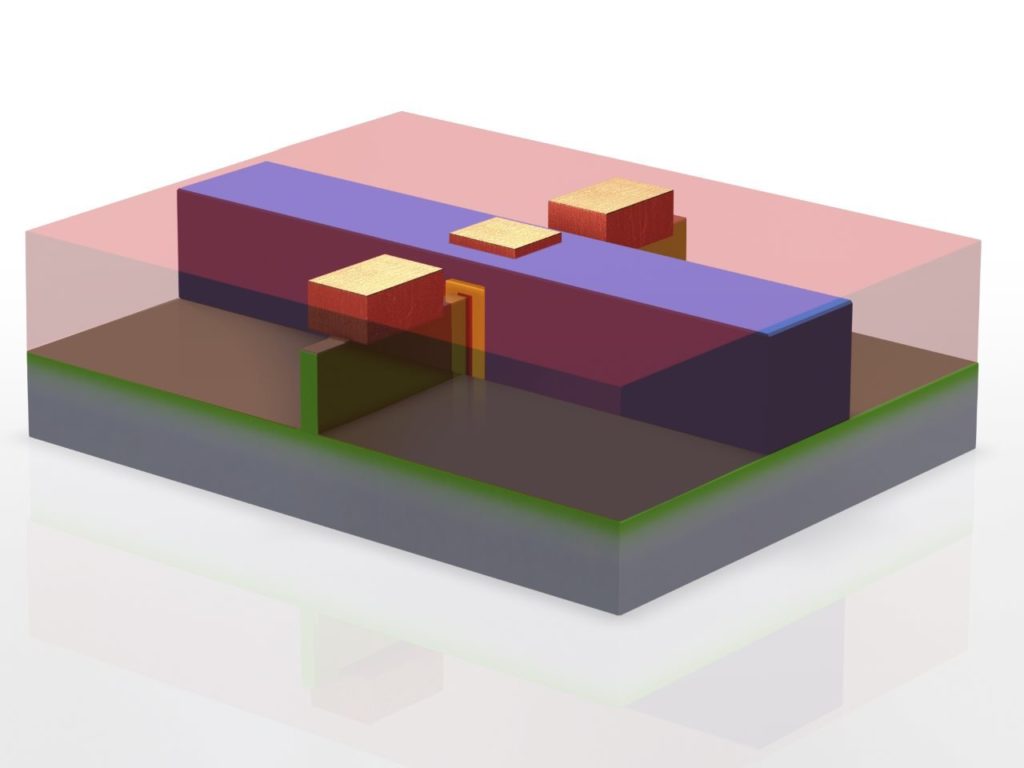

Par photolithographie, une partie du transistor est couvert d’une autre couche photorésistante, et une fine couche de dioxyde de silicium (en rouge) est créée en insérant la galette dans un fourneau rempli d’oxygène, pour faire office de diélectrique temporaire.

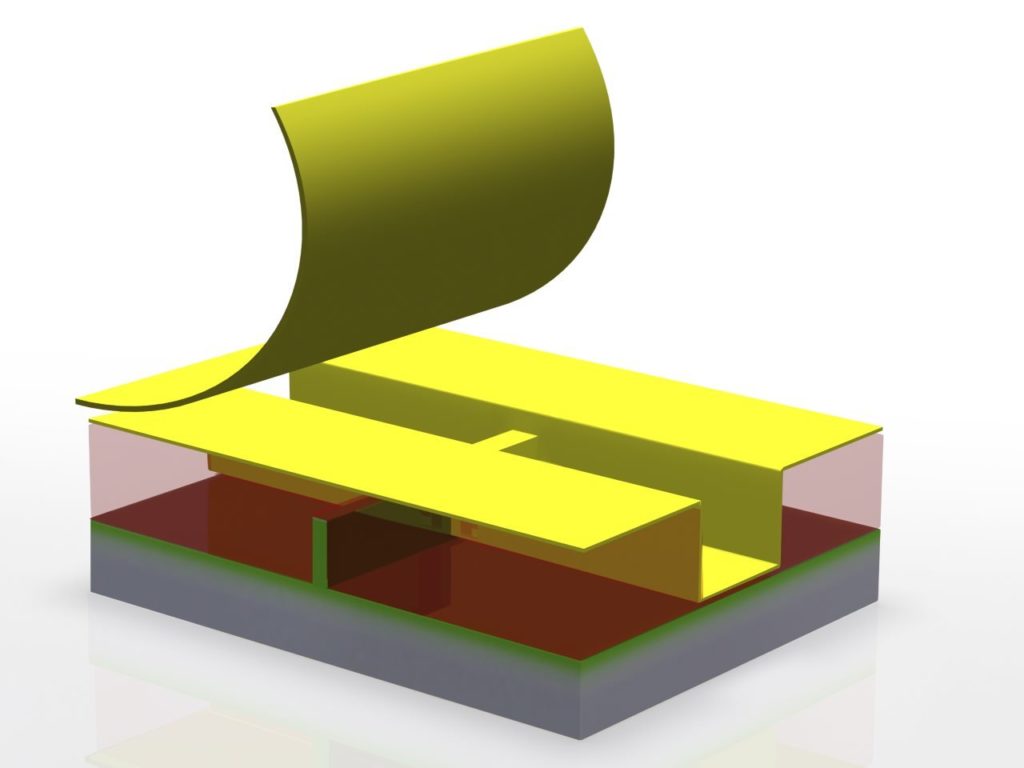

Electrode

Toujours pas photolithographie une couche temporaire de silicium polycristallin est déposée (en jaune), en guise d’électrode.

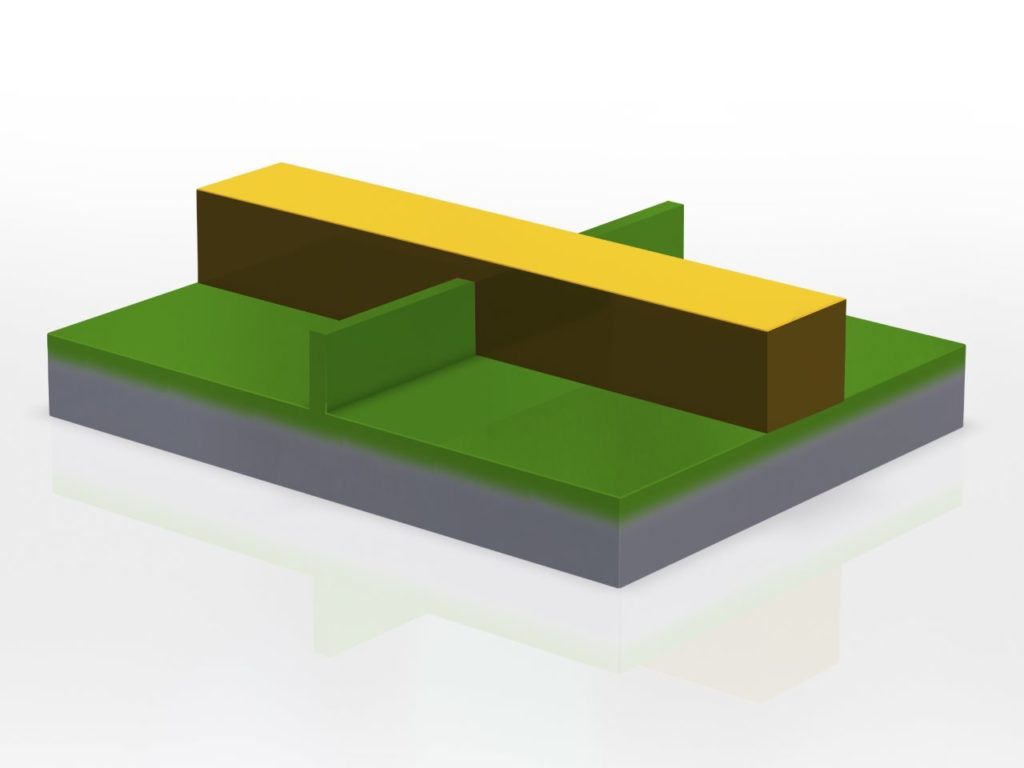

Isolation

Par oxydation, une couche de dioxyde de silicium est ensuite déposée sur la totalité de la galette (en rouge transparent) pour isoler les transistors.

Fin des parties temporaires

A l’aide d’un nouveau masque, on retire les électrodes et diélectriques temporaires. On en arrive au pont final, appelé « Gate Last ».

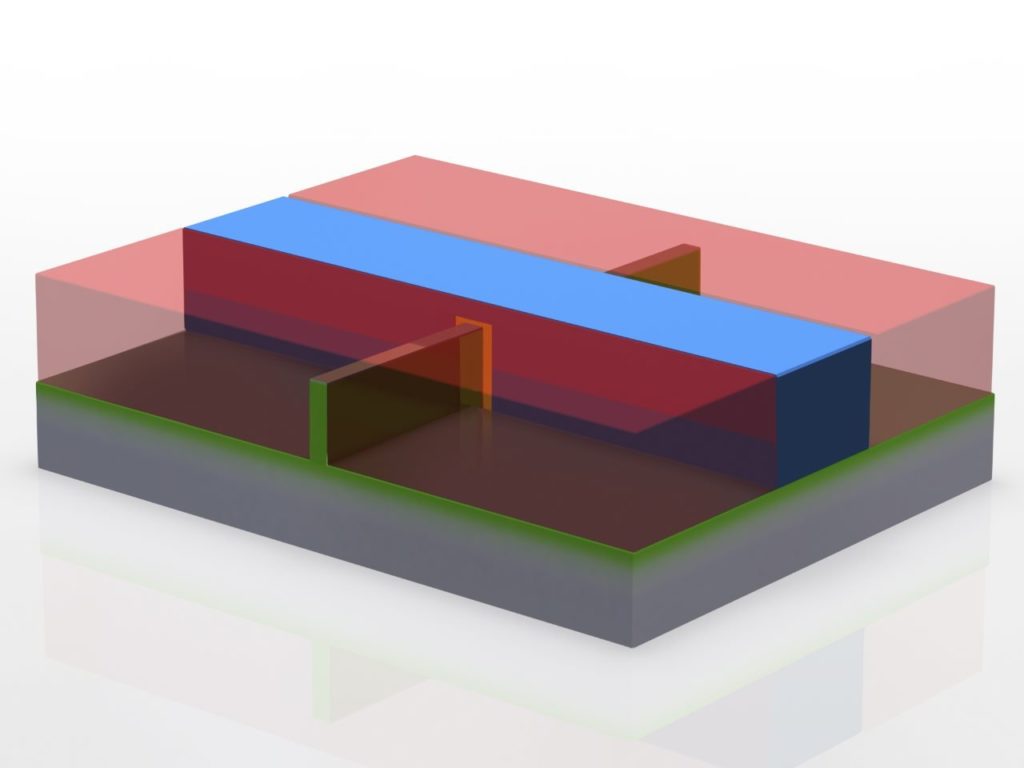

Application du diélectrique High-K

Des couches moléculaires successives sont déposées dans un procédé appelé « atomic layer deposition ». Par un procédé photolithographique, on retire ensuite la plupart de la couche déposée (en jaune), notamment sur l’isolant.

Le pont métal (metal gate)

Il ne reste alors que le diélectrique High-K ici en jaune, à la place du premier diélectrique temporaire. Une nouvelle électrode finale (en bleue) est formée par lithographie sur la galette de silicium (wafer) et retirée de toutes les zones où elle est indésirable. Le transistor High-K metal gate est ainsi beaucoup plus efficace que les précédentes générations, avec moins de fuites de courant.

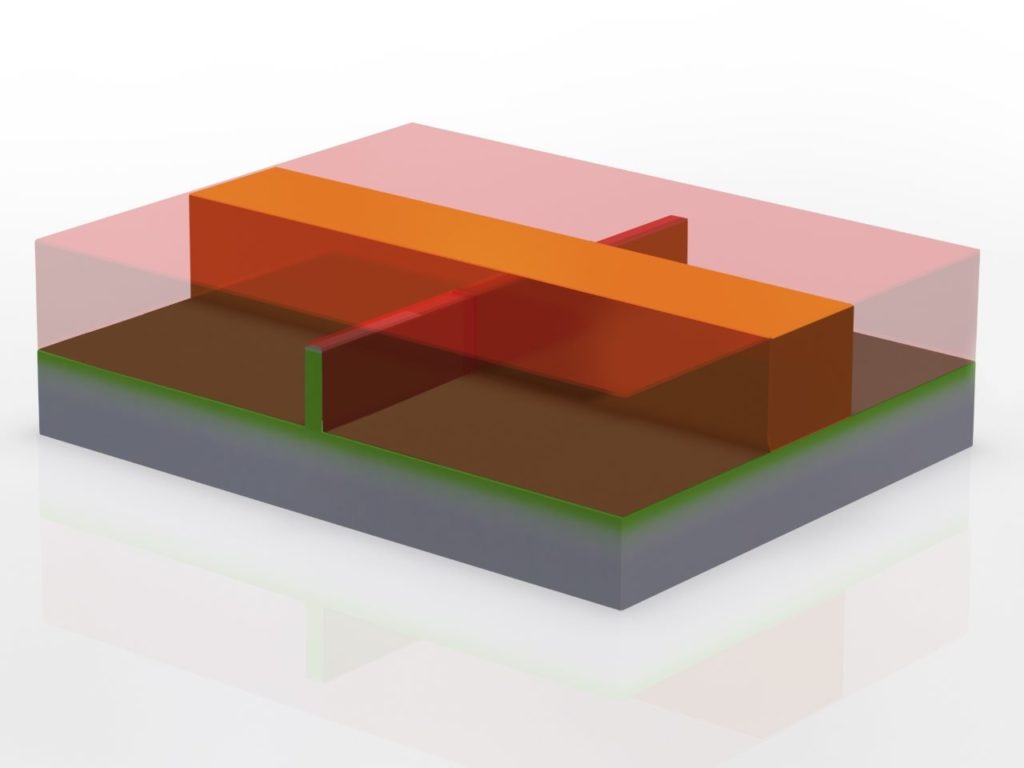

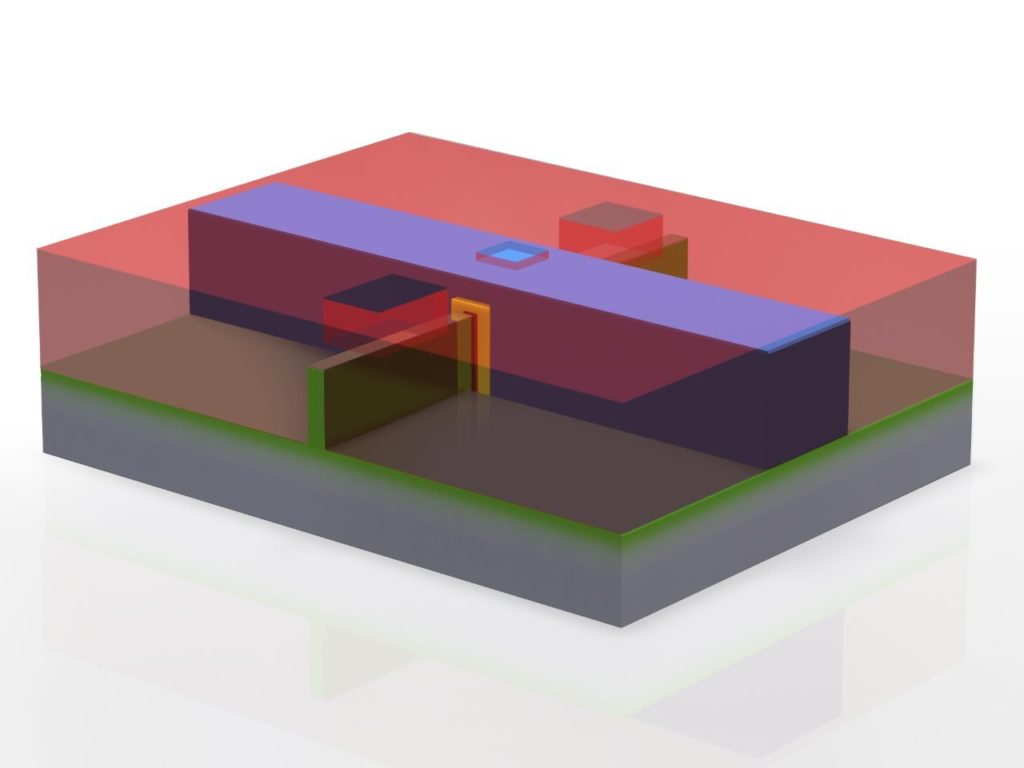

Presque prêt

On en revient à l’étape classique de la finalisation : trois trous sont gravés dans la couche isolante au dessus du transistor, et vont bientôt être bouchés par du cuivre, chargé de les connecter aux autres transistors.

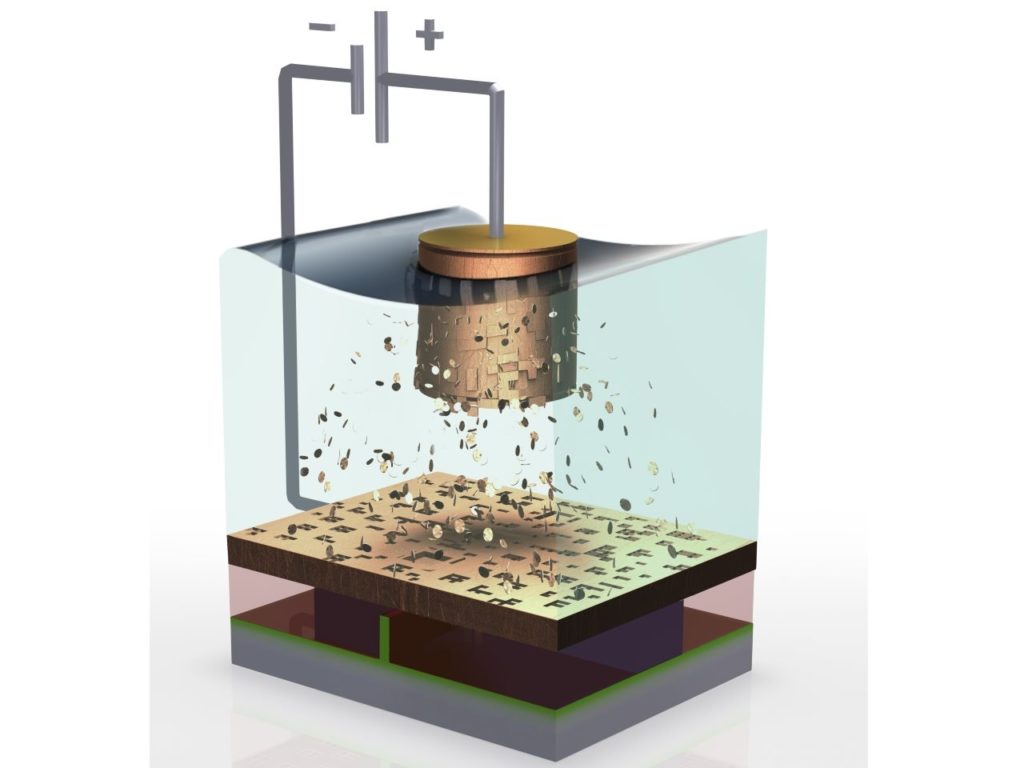

Dépôt Electrolytique

Polissage

Résultat

La couche de cuivre est ainsi éliminée pour ne laisser que le cuivre incrusté dans les trous précédemment percés.

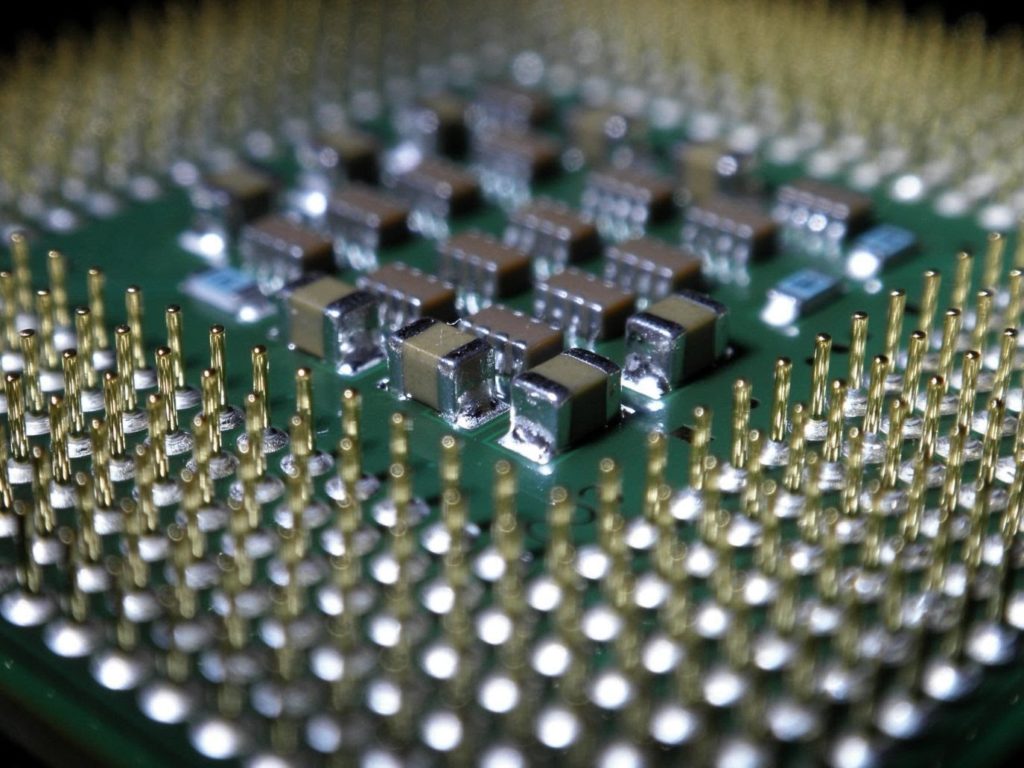

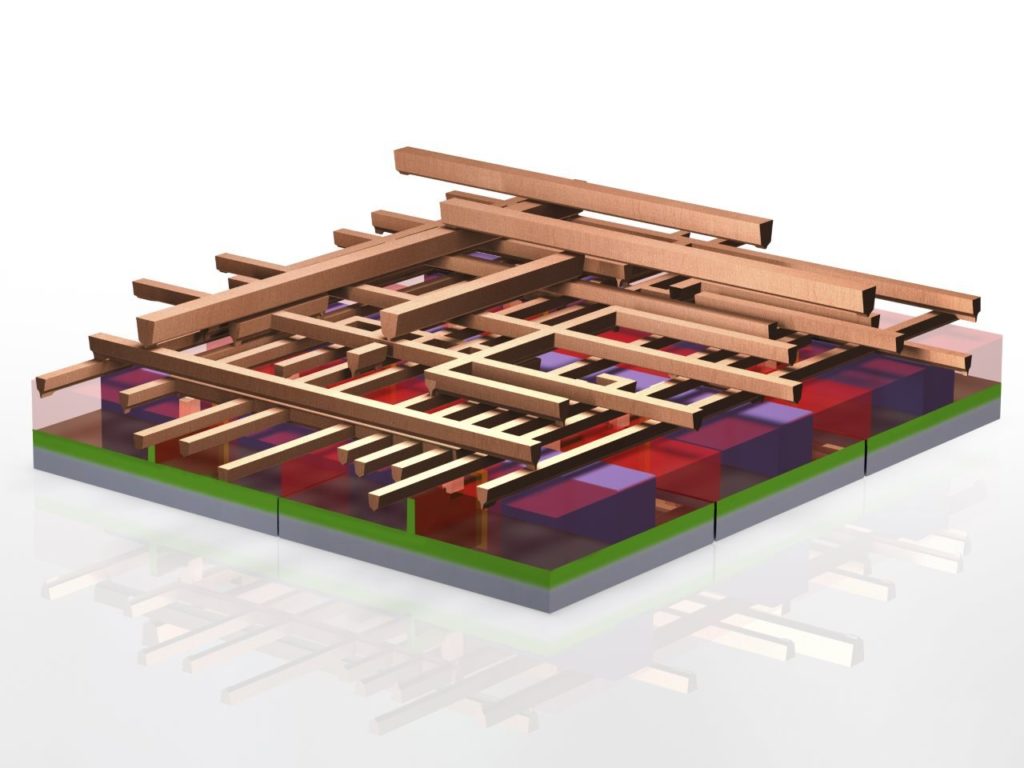

Construction d’un réseau en couches

De nombreuses couches métalliques sont crées pour assurer l’interconnexion des transistors. Le “câblage” de ces connexions varie suivant l’architecture et la conception déterminées pour un type de processeur. Ainsi, l’apparence très plate des processeurs est trompeuse : le circuit complexe peut être composé de plus de vingt couches superposées. Si l’on regarde un processeur de plus près, le réseau de circuits et transistors imbriqués peut faire penser à un échangeur d’autoroute multi-étages futuriste…

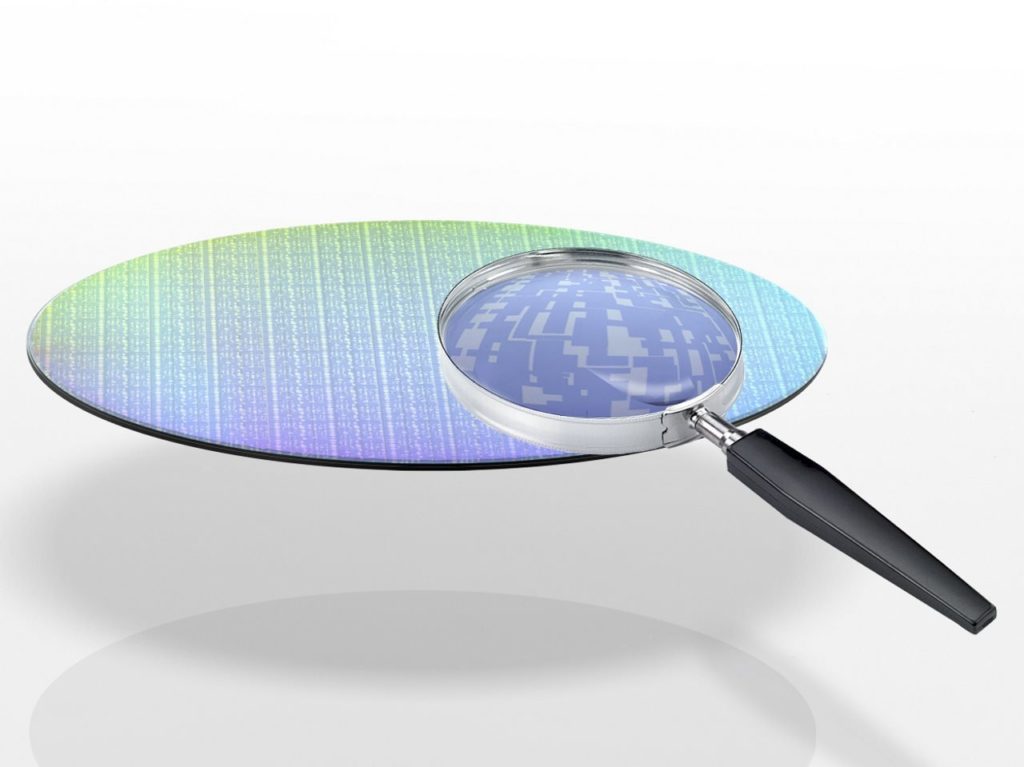

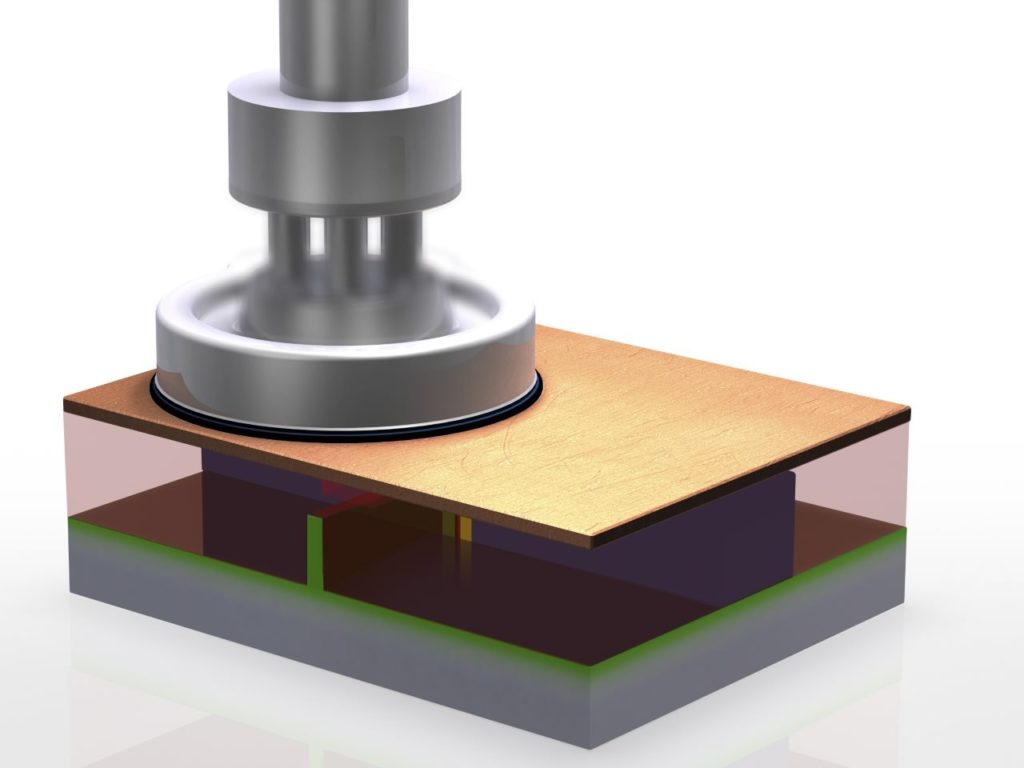

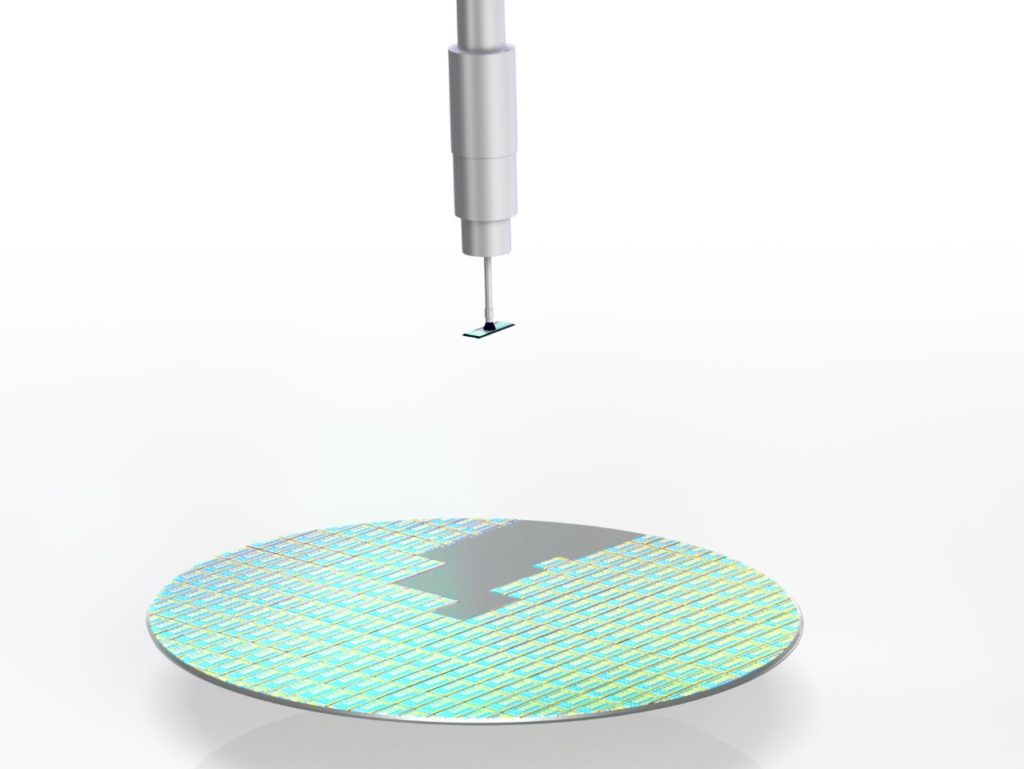

Tri des wafers

Cette portion d’un wafer passe à l’épreuve d’un premier test de fonctionnement : chaque puce reçoit plusieurs types de signaux-test qui sont alors suivis et comparés aux “bonnes réponses”.

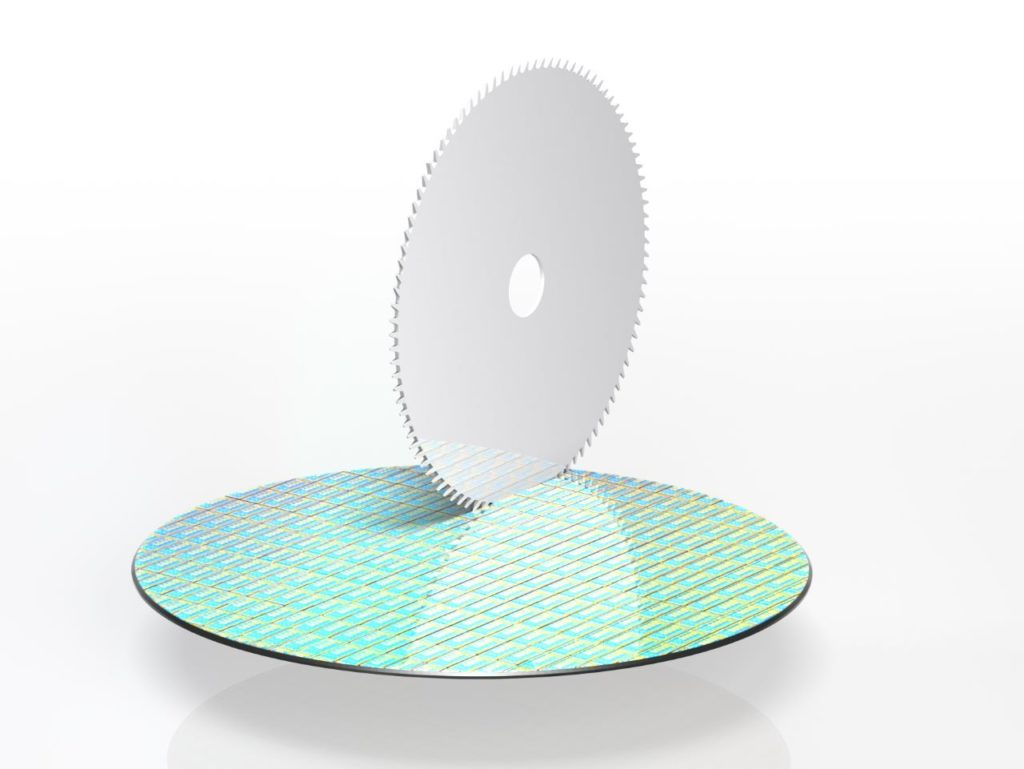

Découpage du wafer

Une fois que le rendement (le fameux yield) de processeurs aptes à fonctionner a été déterminé, le wafer est découpé en morceaux que nous connaissons bien sous le nom “dies”.

Le bon, la brute et le truand

Les dies qui passent les tests avec succès passent à l’étape de l’encapsulation (packaging), tandis que ceux qui ont échoué sont jetés. Il y a quelques années, Intel en faisait des porte-clés. On se souvient que ce concept a été repris il y a quelques mois par NVIDIA.

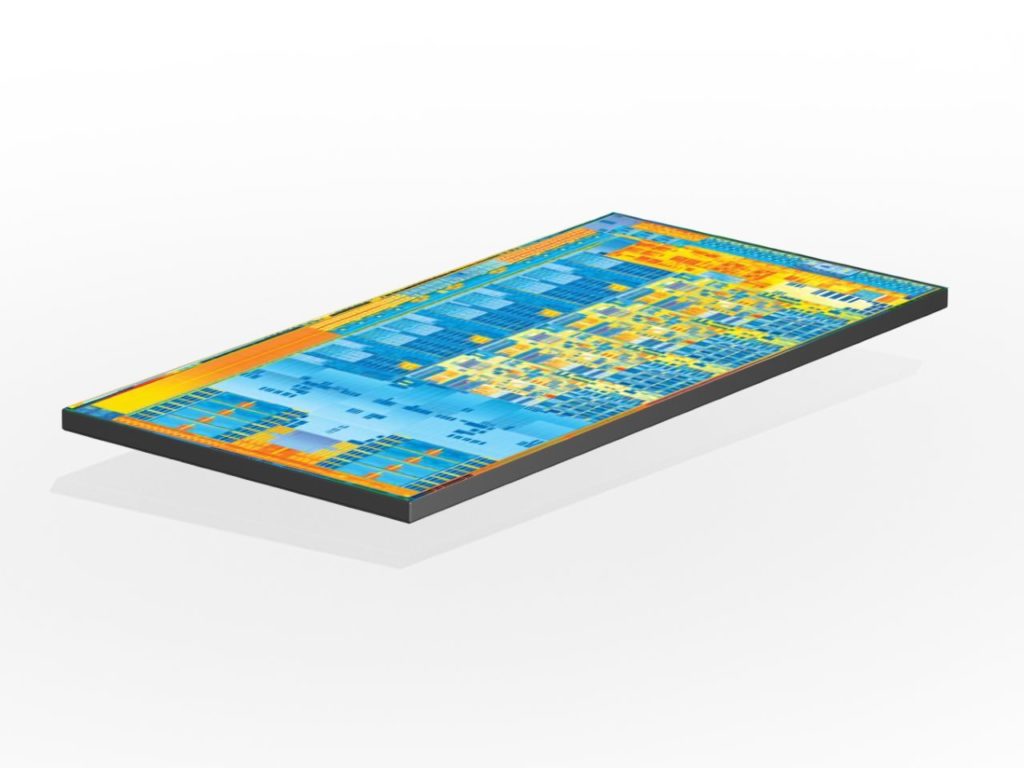

Zoom sur le die

Voici donc le résultat du découpage, le die d’un processeur (ici un Core i7).

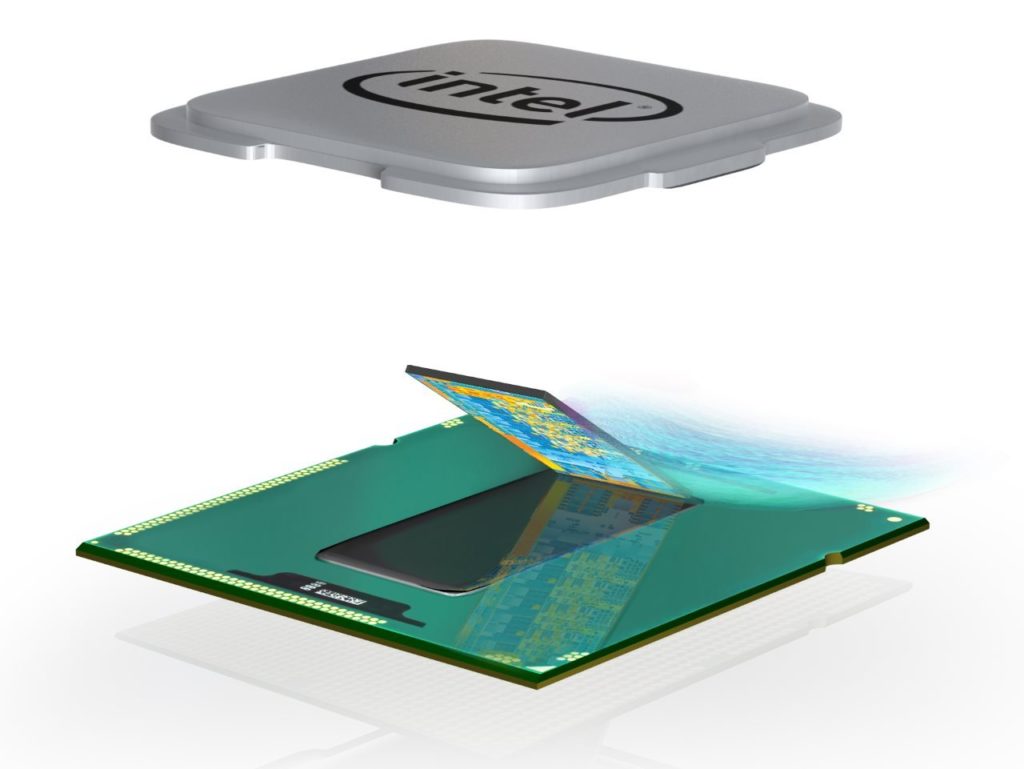

Encapsulation

Le substrat, le die et le heatspreader sont assemblés pour aboutir au processeur dans sa forme finale. Relié au socket de la carte mère, le substrat vert joue un rôle d’interface électrique et mécanique entre le processeur et le reste des composants. La capsule (heatspreader) est quant à elle l’interface thermique sur laquelle la solution de refroidissement est appliquée. Certains d’entre nous n’hésitent pas à la polir au papier de verre pendant des heures pour optimiser la surface d’échange, voir à la retirer, ce qui reste très dangeureux et plus vraiment intéressant désormais.

Le processeur, roi des produits finis

Les microprocesseurs sont les produits manufacturés les plus complexes au monde. Il est important de noter que leur fabrication se fait au travers d’une centaine d’étapes, seules les plus importantes ont donc été représentées depuis le début de ce reportage photo.

Phase de test terminale

S’il y a bien une étape à laquelle on voudrait assister pour faire son choix, c’est ici : les processeurs sont testés par rapport à leurs caractéristiques principales, parmi lesquelles dissipation et fréquence maximale.

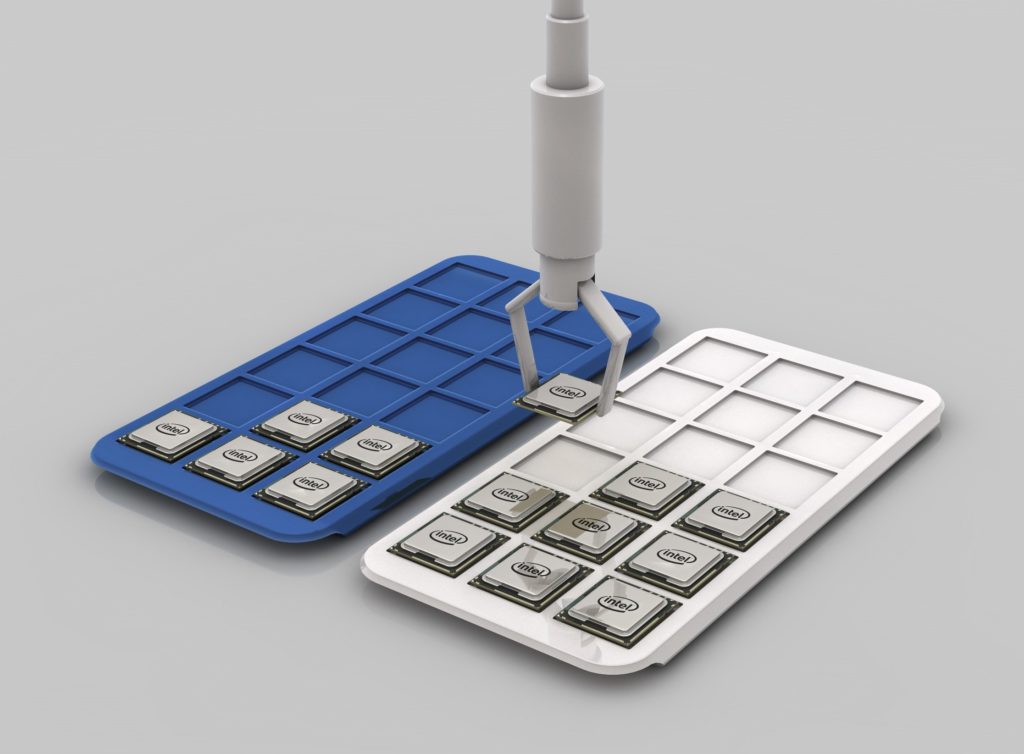

Répartition des processeurs

Suivant les résultats des tests par classe de CPU, les processeurs ayant les mêmes capacités sont disposés sur une palette de transport commune. Cette étape est qualifiée de “binning” : on détermine alors la fréquence maximale, ce qui permet de les trier par lot (batch) pour finalement les vendre en fonction des spécifications stables validées.

Direction revendeurs

Au final, les processeurs sont envoyés nus aux assembleurs ou bien en version boîte pour la vente directe au consommateur.

Nous remercions Intel de nous avoir fourni les illustrations de ce reportage photo, ainsi que le texte en anglais, lequel a été adapté. Ces illustrations en grand format ainsi que le texte original sont disponibles sur le site du fabricant. Si l’anglais ne vous rebute pas, Global Foundries a de son côté réalisé un très bon documentaire sur le même thème.