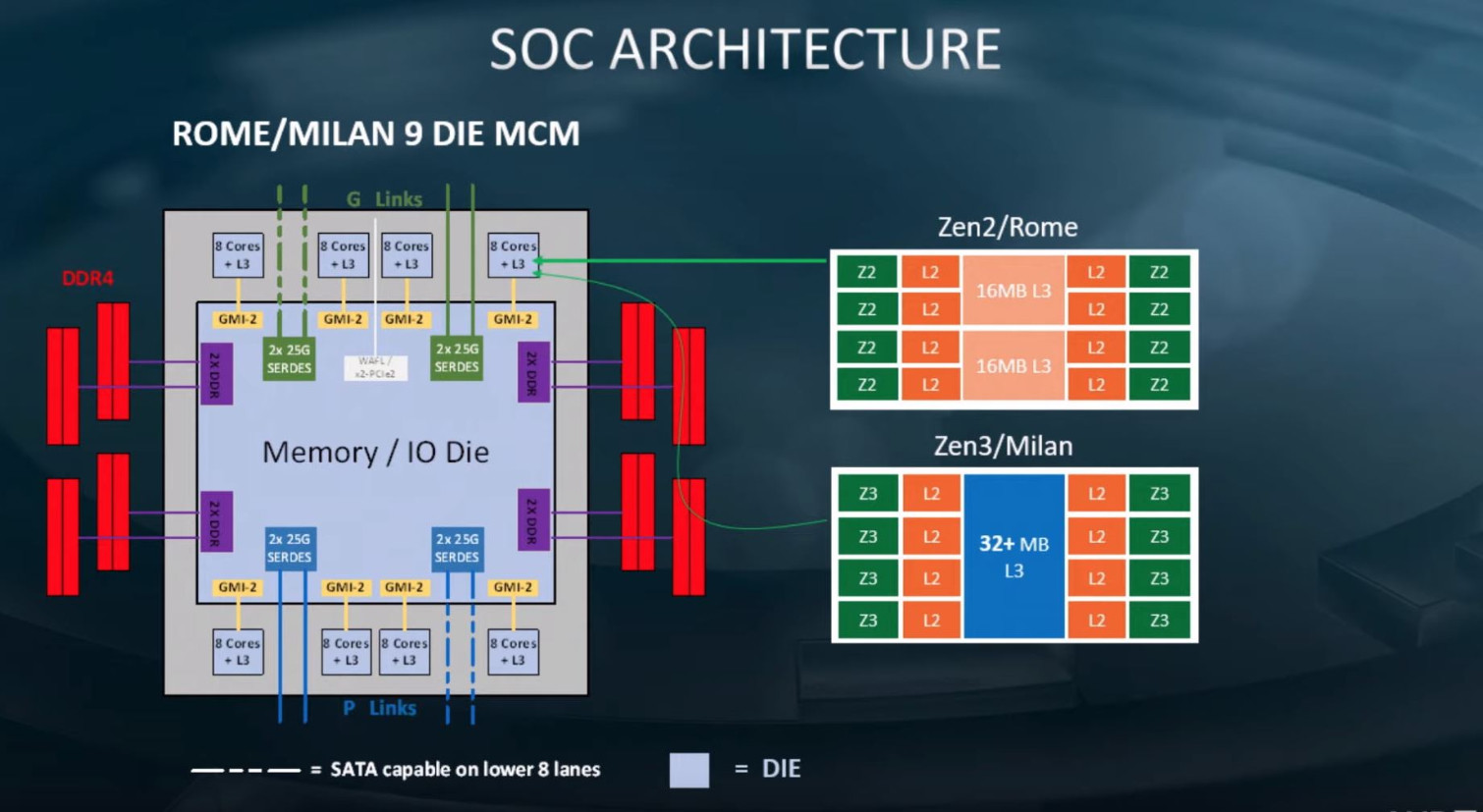

Cette mémoire unifiée permettrait de réduire la latence au sein du chiplet, en supprimant les communications entre CCX.

Avec ses prochains processeurs Milan pour serveurs, AMD envisagerait de se débarrasser des CCX en passant à Zen3, en optant pour un cache L3 de 32 Mo unifié entre les huit coeurs d’un chiplet (CCD). L’agencement global ne changerait pas, puisqu’on retrouverait huit chiplets, une puce d’E/S et huit cœurs pour chaque chiplet.

Les actuels CCX désignent un groupe de quatre cœurs CPU avec leurs caches (L1, L2, L3). Dans un chiplet (CCD), deux CCX communiquent entre eux via l’interface Infinity Fabric. L’unification des 32 Mo de mémoire cache pourrait ainsi supprimer la latence de cette interconnexion entre deux CCX.

2 threads par cœur, et pas 4

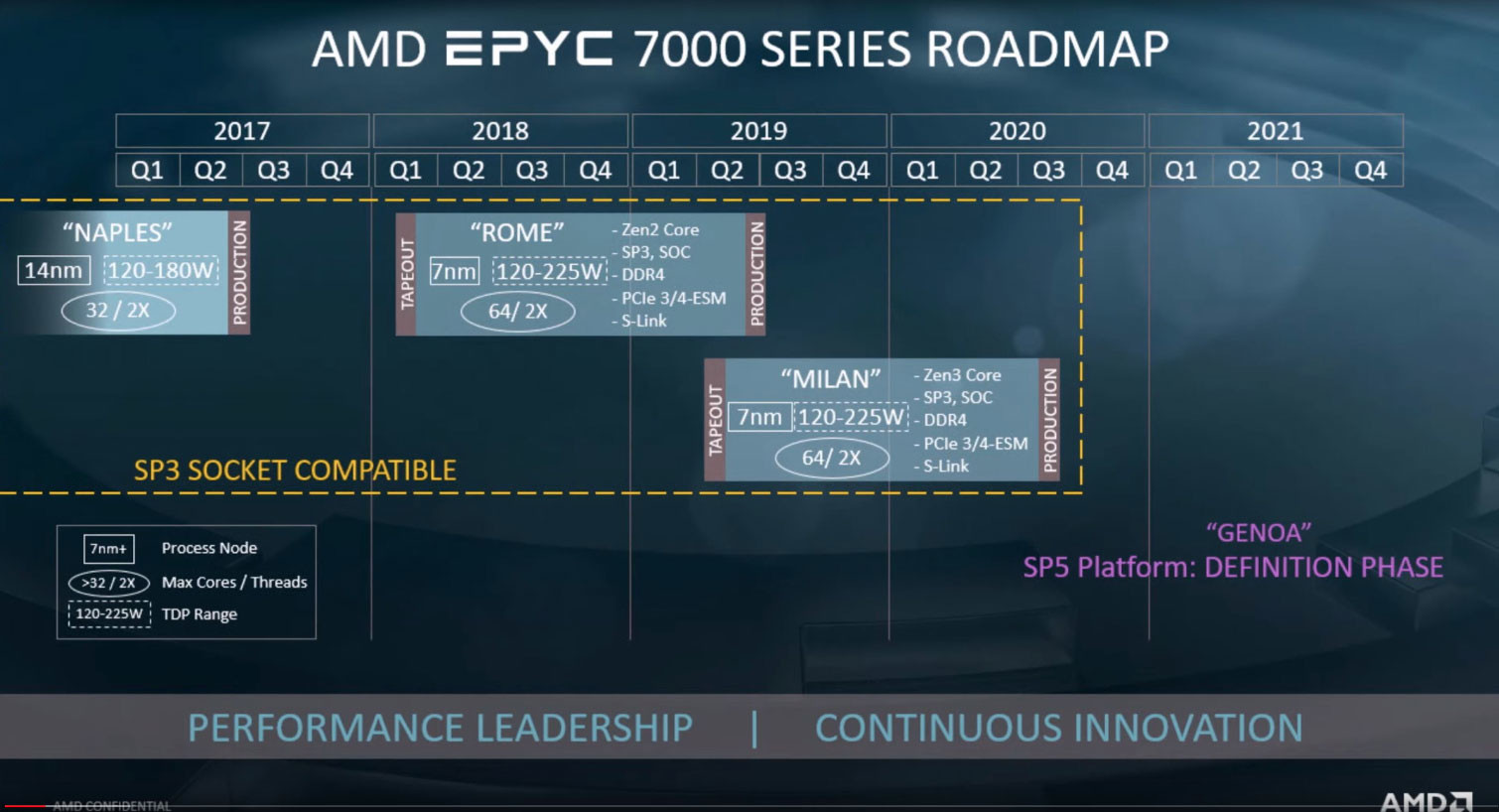

Les processeurs Zen 2 sont sur le devant de la scène depuis plusieurs mois maintenant, et certains modèles phares, comme le Ryzen 9 3950X ne sont pas encore sortis. Pas de quoi ralentir le rythme d’AMD, dont les CPU Zen3 et Zen4 pourraient débarquer dès 2020 et 2021.

AMD a partagé ces informations lors de la conférence HPC-AI Advisory Council UK. Elles ont ensuite été divulguées sur YouTube avant d’être retirées. Tom’s Hardware US a toutefois eu le temps de capturer quelques images. Parmi les autres fuites, il était également question du SMT : il y aurait bien 2 threads par coeur, et pas 4, ce qui infirmerait la rumeur du des 4 threads par cœur physique pour Zen3. Il faudra peut-être attendre Genoa et Zen4 pour voir cette évolution débarquer.

Enfin, rappelons que l’architecture Zen3 profitera d’un procédé de gravure en 7 nm+ EUV de chez TSMC.