Une puce susceptible d’engloutir 600 W qui requiert un refroidissement par watercooling.

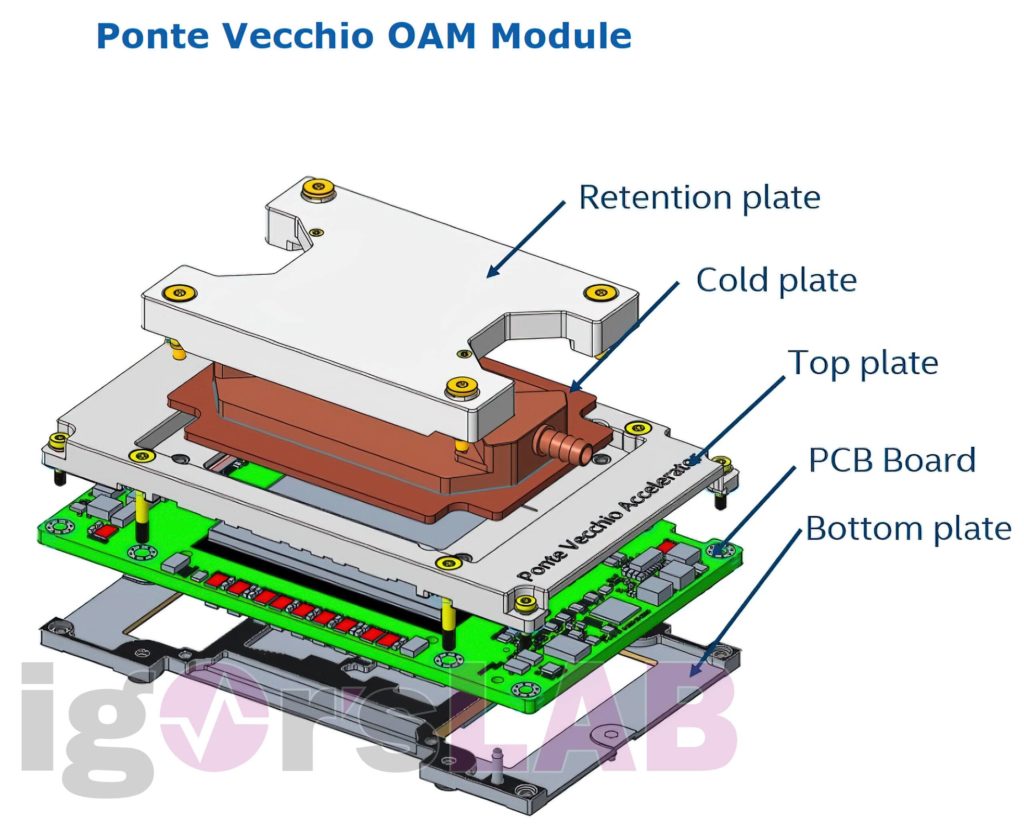

Raja Koduri nous avait déjà appris que le GPU Intel Ponte Vecchio, le plus puissant des GPU pour supercalculateurs conçus par l’entreprise, possédait 100 milliards de transistors et 47 ‘Magical Tiles’. En outre, pur dissiper la chaleur dégagée par cette puce, capable d’engloutir plus de 600 W, il avait aussi mentionné un système de refroidissement liquide. Igor Wallossek a partagé quelques schémas inédits d’une solution GPU Ponte Vecchio OAM (OCP Accelerator Module).

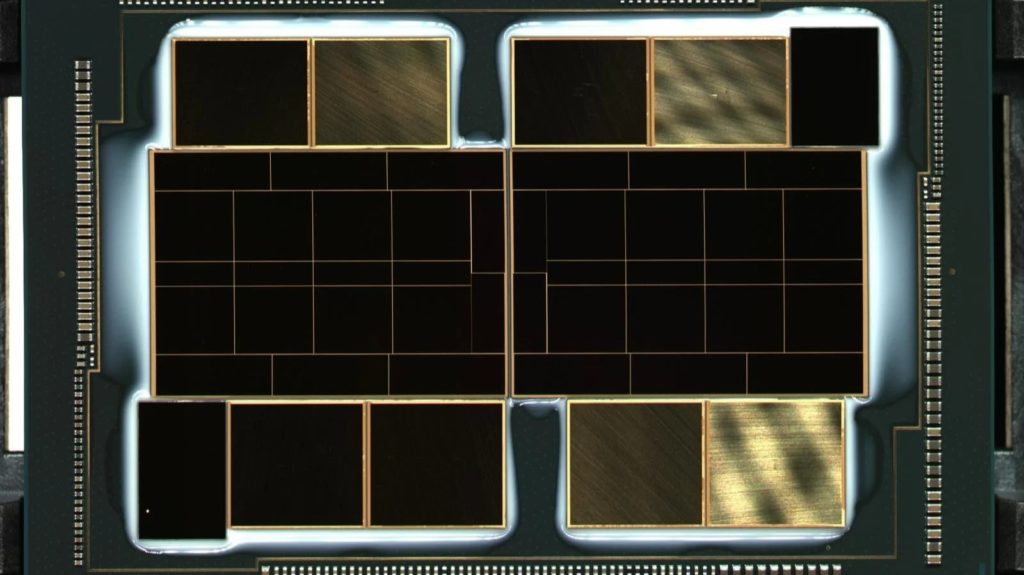

Dans un premier temps, notre confrère confirme que le GPU Ponte Vecchio hérite d’une conception hétérogène avec différents nœuds de gravure. Certaines parties du GPU se basent sur le nœud 10 nm SuperFin puis, à terme, 7 nm d’Intel ; d’autres sur les nœuds 7 nm (provisoirement) et 5 nm de TSMC. Tous ces éléments sont interconnectés grâce à la technologie Foveros.

La conception détaillée

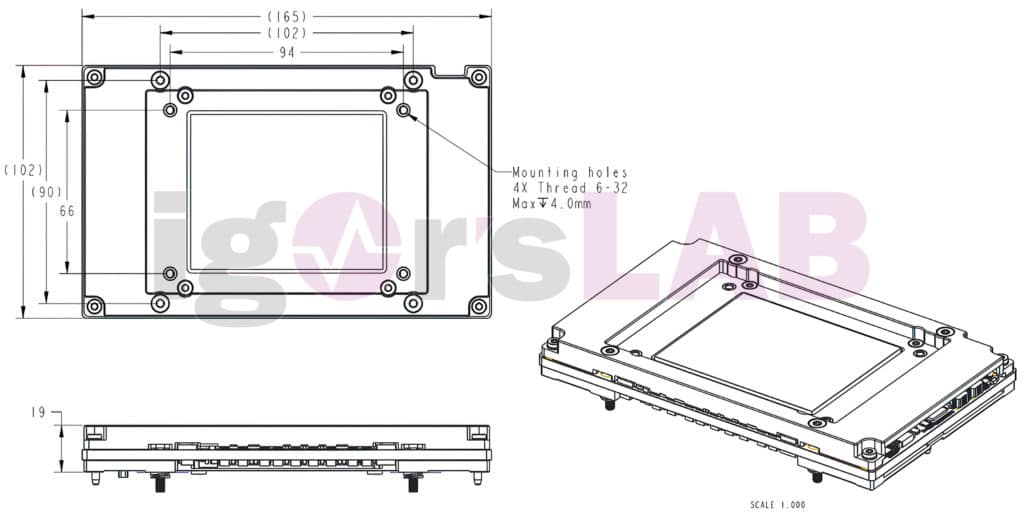

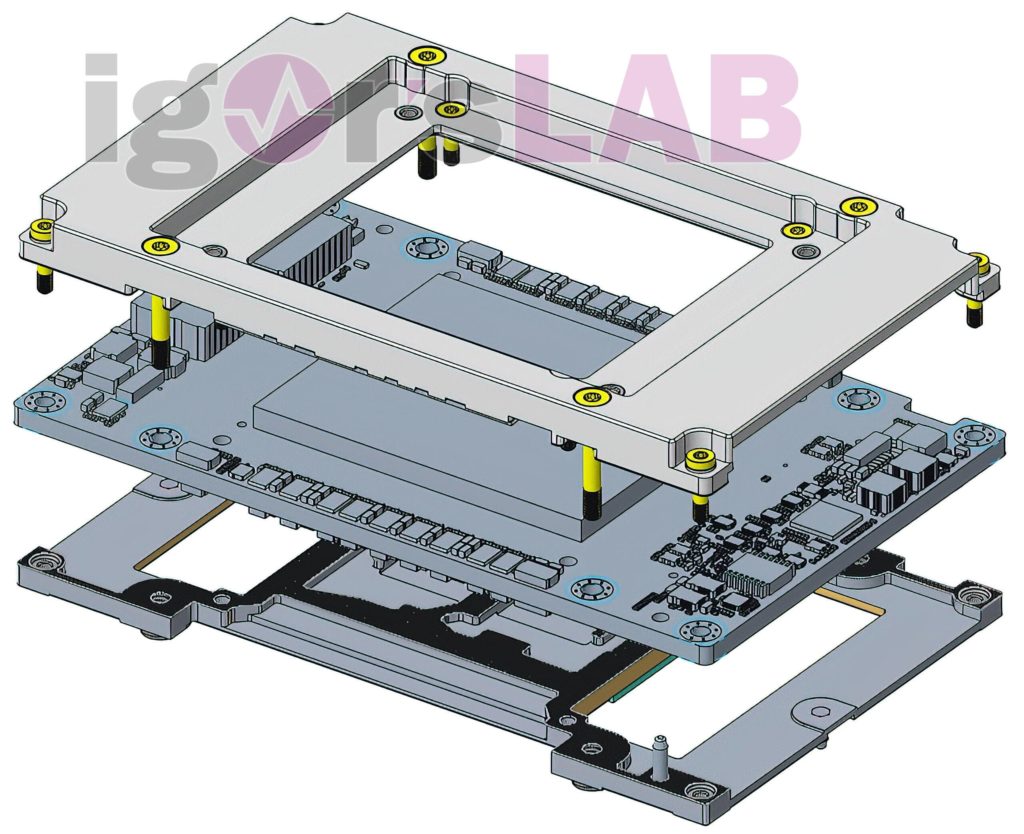

Igor Wallossek livre également des images d’illustration d’un GPU Ponte Vecchio installé dans un facteur de forme OAM. Le croquis du kit de montage renseigne des dimensions de 102 x 165 mm. Un autre schéma témoigne de la composition de la plaque inférieure, du PCB et de la plaque supérieure. Enfin, la dernière image montre la conception complète.

Selon Raja Koduri, le GPU Ponte Vecchio a une puissance de calcul FP16 de 1 PFLOPS (1 000 TFLOPS). À titre de comparaison, l’A100 de NVIDIA offre 312 TFLOPS en FP16. Au sujet de la composition des 47 Magical Tiles, il y aurait 2 tiles principales produites par Intel en 10 nm SuperFin ; 16 tiles dédiées au calcul fabriquées par TSMC en 7 nm ; 8 tiles cache « Rambo » ; 11 tiles EMIB (Embedded Multi-Die Interconnect Bridge) ; 2 tiles I/O ; 8 tiles de mémoire HBM.

Source : Igor’s Lab