Des détails sur l’interconnexion entre ce cache 3D vertical et le CCD.

Au fil des semaines, nous glanons des informations sur la technologie 3D V-Cache d’AMD présentée pour la première fois début juin. À l’époque, Lisa Su avait présenté un Ryzen 5000 à 12 cœurs doté de ce fameux cache 3D vertical lui octroyant 64 Mo de mémoire cache L3 en plus ; un surplus qui lui permettait d’offrir des performances 15 % supérieures en moyenne dans les jeux selon la PDG d’AMD. Depuis, l’entreprise a fourni quelques détails supplémentaires par le biais d’une vidéo. Les données du jour proviennent de Yuzo Fukuzaki de TechInsights.

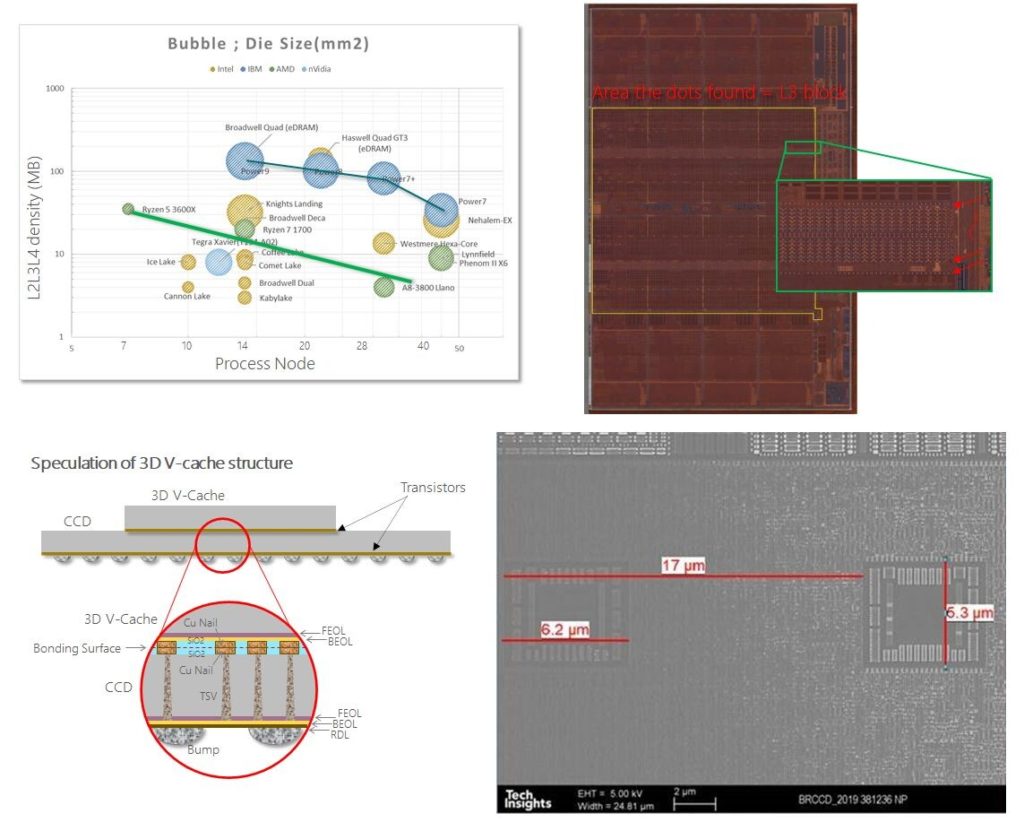

Ce dernier nous apprend que les CPU Zen 3 ont été élaborés, dès le départ, avec l’idée de leur accoler un tel cache. C’était évident, mais cela confirme qu’AMD travaille sur cette technologie depuis plusieurs années. Yuzo Fukuzaki a partagé l’image ci-dessus d’un Ryzen 9 5950X standard où figure les emplacements pour les TSV (Through Silicon Vias). Les caches 3D, un par CCD (Core Complex Die), peuvent ajouter 64 Mo de cache L3 chacun. Ainsi, en l’état, cette technologie ouvre la voie à des processeurs pouvant embarquer jusqu’à 192 Mo de cache (64 x 2 + 32 x 2).

Kioxia teste de la mémoire 3D NAND à 6 bits par cellule

KoZ de 6,2 x 5,3 μm

En pratique, le 3D V-Cache prend la forme d’une puce SRAM de 64 Mo, fabriquée en 7 nm comme les CCD Zen 3. C’est un die carré de 36 mm² (6 x 6 mm) qui vient se positionner au-dessus du CCD. D’après Yuzo Fukuzaki, il est relié au CCD par environ 23 000 TSV. Le pas des TSV avoisinerait les 17 µm. Le KoZ (Keep out Zone) serait de 6,2 x 5,3 μm. Par ailleurs, la bande passante s’élèverait à 2 To/s. Enfin, au niveau du système, cette mémoire cache L3 supplémentaire serait utilisable de manière totalement transparente.

AMD prépare des APU basés sur l’architecture graphique RDNA