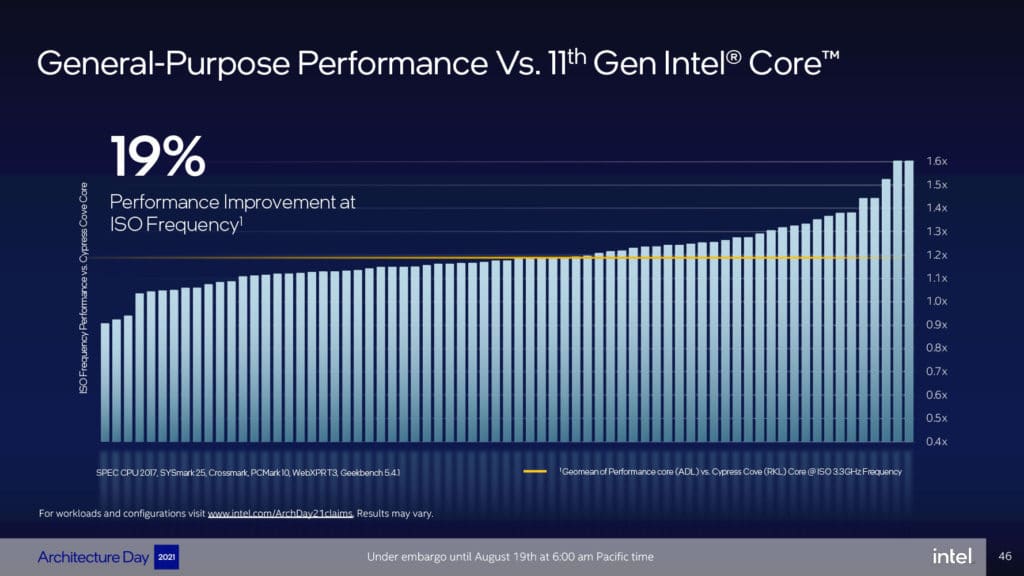

Intel annonce un gain d’IPC de 19 % pour Alder Lake-S par rapport à la génération Rocket Lake-S.

Dans le cadre de l’Intel Architecture Day 2021, l’entreprise a fourni des détails sur ses prochains processeurs Alder Lake et Xeon Sapphire Rapids, ainsi que sur ses GPU HPG Alchemist et Xe HPC “Ponte Vecchio”. Nous traiterons ici les informations relatives aux CPU ; vous trouvez les données relatives aux GPU dans un second dossier.

Des gammes desktop / mobile réunifiées

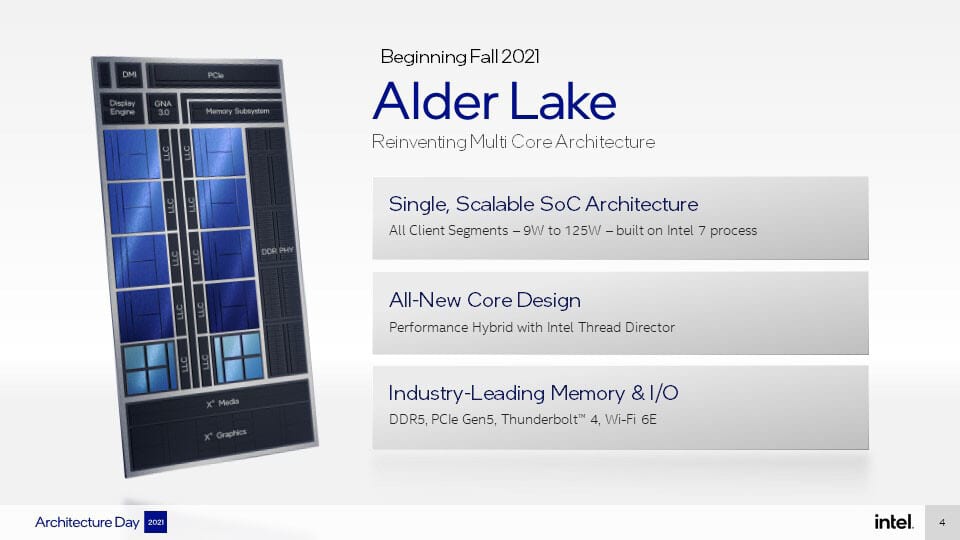

Commençons par les puces destinées au grand public : la douzième génération de Core, nommée Alder Lake, et qui sera commercialisée à l’automne 2021. Comme prévu, celle-ci implique une conception hybride qui associe deux types de cœurs CPU ; une première pour un processeur x86 desktop.

Pour Intel, cette 12e génération est également l’occasion d’unifier ses gammes mobile et bureau. En effet, depuis la 9e génération, les processeurs s’appuient sur des IP et des nœuds de gravure différents selon les plateformes. Les puces mobiles étaient bâties autour des architectures Ice Lake (10 nm) / Comet Lake (14 nm) puis Tiger Lake ; les puces desktop héritaient d’un nœud de gravure en 14 nm dans le cadre des architectures Comet Lake-S et Rocket Lake-S successivement. Avec la 12e génération, tous les processeurs de ces deux segments seront donc logés à la même enseigne : Intel va décliner son architecture Alder Lake basée sur le nœud Intel 7 (anciennement 10 nm Enhanced SuperFin) à la fois pour les versions mobiles et desktop, sur une plage de TDP allant de 7 W à 125 W.

Trois formats de dies

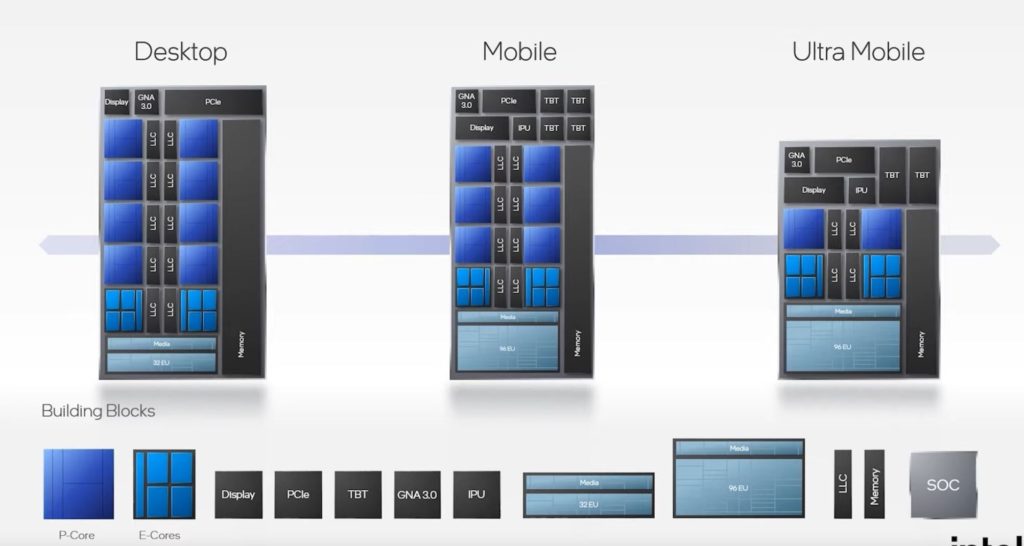

Toutefois, cela ne signifie pas que tous les processeurs se ressemblent. Comme illustré ci-dessous, il y a trois formats de dies ; ils impliquent des disparités en matière de nombre de cœurs CPU et de cœurs graphiques. Les modules P-Core renferment un cœur haute performance Golden Cove ; les modules E-Core contiennent 4 cœurs Gracemont, les cœurs basse consommation. Dans tous les cas, les trois dies peuvent accueillir deux modules E-Core, soit 8 cœurs Gracemont, et embarquent un module GNA 3.0 (Gaussian Network Accelerator) nécessaire au fonctionnement de DLBoost.

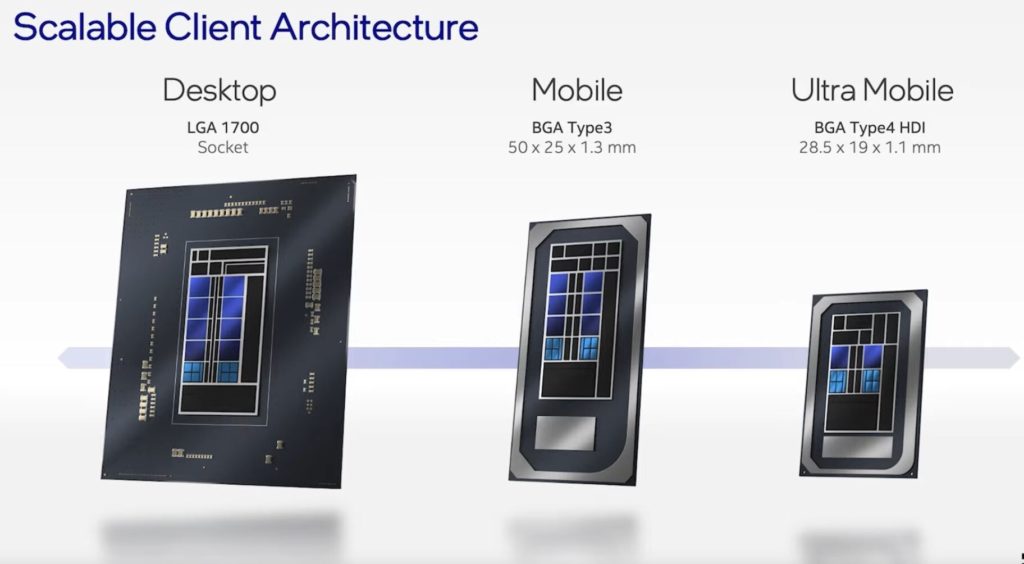

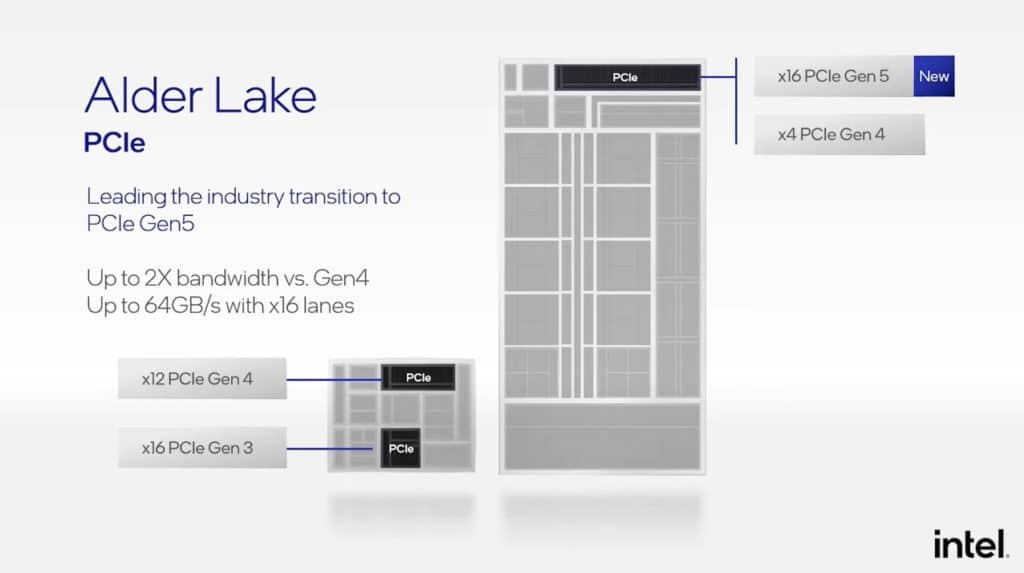

Les processeurs de bureau inaugurent un socket LGA1700 dont les dimensions sont de 37,5 x 45 mm. Ils embarquent jusqu’à 8 cœurs Golden Cove. L’iGPU Xe LP se contente de 32 UE contre 96 UE pour les deux variantes mobiles ; des fréquences plus élevées devraient néanmoins permettre de combler ce déficit. Les processeurs Alder Lake-S gèrent 16 lignes PCIe Gen 5 et 4 lignes PCIe Gen 4 ainsi que la mémoire DDR5 et DDR4 (DDR5-4800 en dual-channel).

Les puces mobiles avec TDP de 28 à 45 W sont conçues dans un boîtier BGA de type 3 qui mesure 50 x 25 x 1,3 mm. Leur die offre suffisamment de place pour 6 cœurs Golden Cove. Ces processeurs gèrent la mémoire DDR5 et LPDDR5 en dual-channel tout en conservant le support de la DDR4 et LPDDR4 ; ils profitent aussi d’une interface PCIe Gen5. Quatre contrôleurs Thunderbolt 4 sont également présents.

Enfin, les processeurs pour ultra-portables (7 à 28 W) impliquent un boîtier BGA de type 4 (28,5 x 19 x 1,1 mm). Leur nombre de cœurs Golden Cove se limite à deux. En outre, contrairement aux deux précédentes plateformes, seule l’interface PCIe Gen4 est ici supportée. Pas de discrimination concernant la mémoire : DDR5, LPDDR5, DDR4 et LPDDR4.

Un gain d’IPC de 19 % pour Golden Cove

Terminons sur Alder Lake par quelques mots sur les performances. Selon Intel, les cœurs Golden Cove des processeurs Alder Lake-S offrent un gain d’IPC de 19 % à fréquence égale par rapport aux cœurs Cypress Cove des actuelles puces Rocket Lake-S.

Noctua fournira gratuitement des kits de montage LGA1700 pour ses dissipateurs CPU

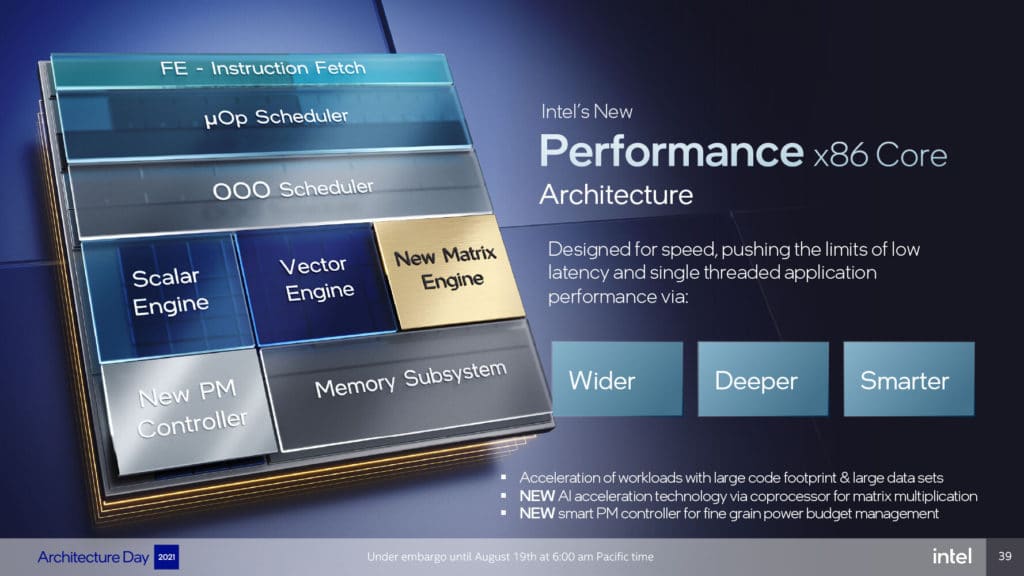

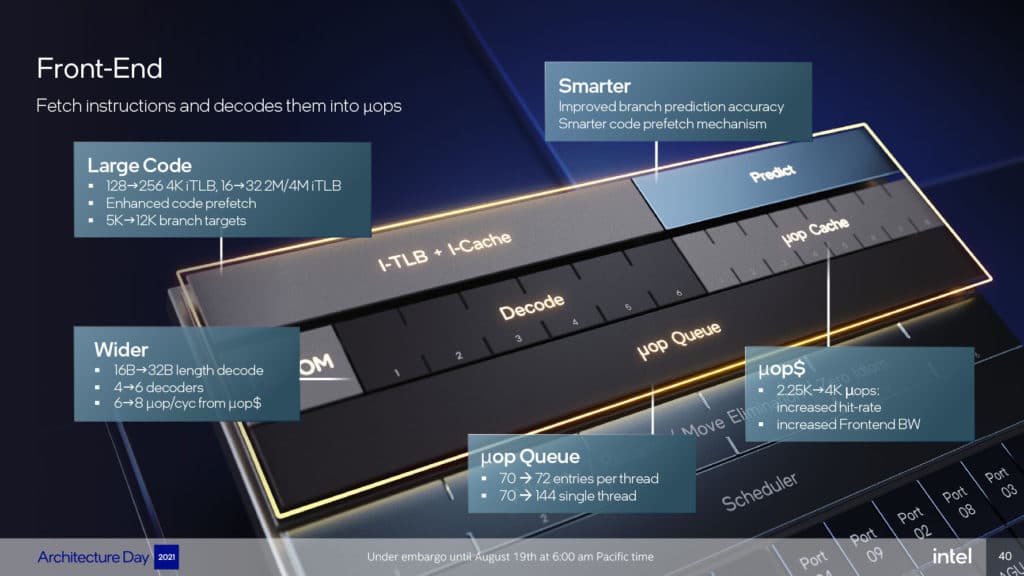

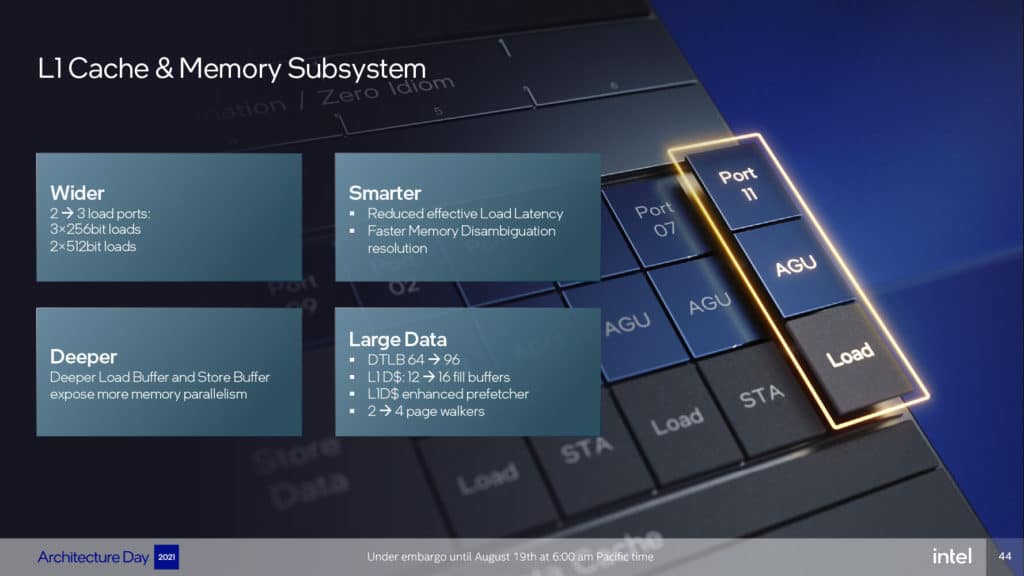

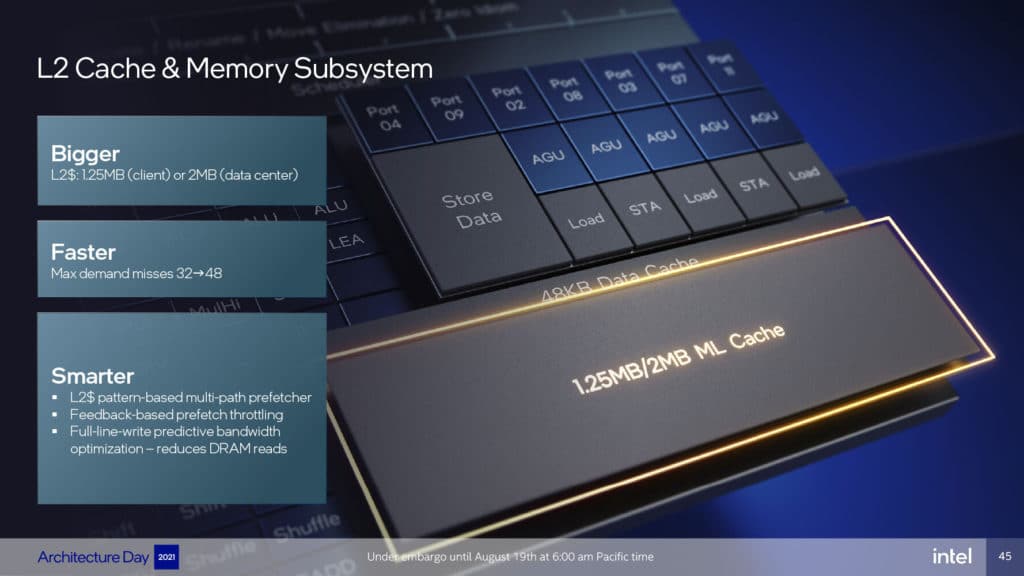

Intel justifie cette hausse par diverses améliorations apportées aux cœurs CPU, détaillées dans la documentation ci-dessous. Mentionnons par exemple une taille de cache L2 qui passe à 1,25 Mo pour les processeurs grand public et à 2 Mo pour les versions serveurs/HEDT. C’est une belle hausse par rapport aux 512 Ko des cœurs CPU Cypress Cove, même si les puces Tiger Lake-U bénéficiaient déjà de cette quantité de cache L2.

Xeon Sapphire Rapids

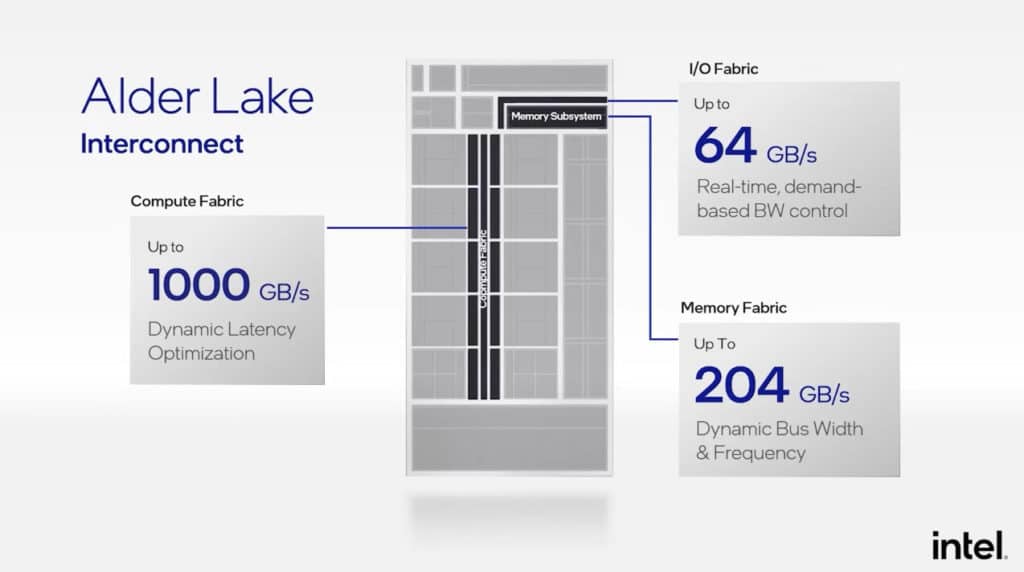

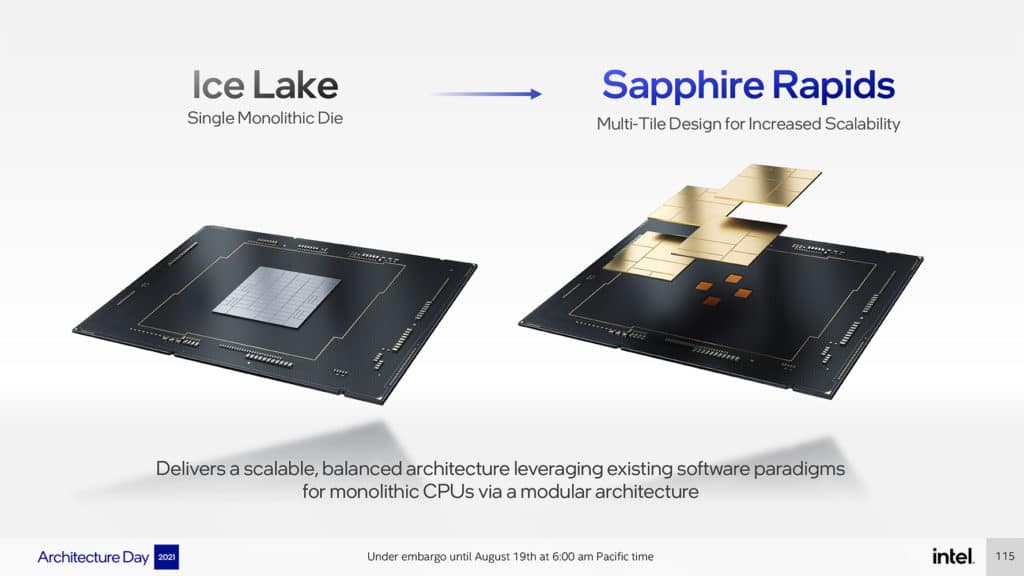

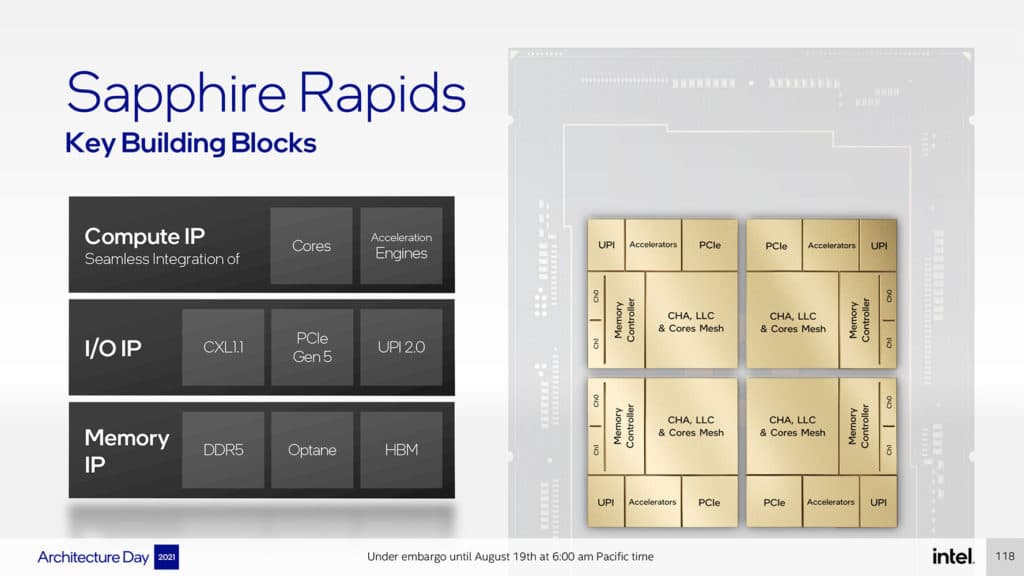

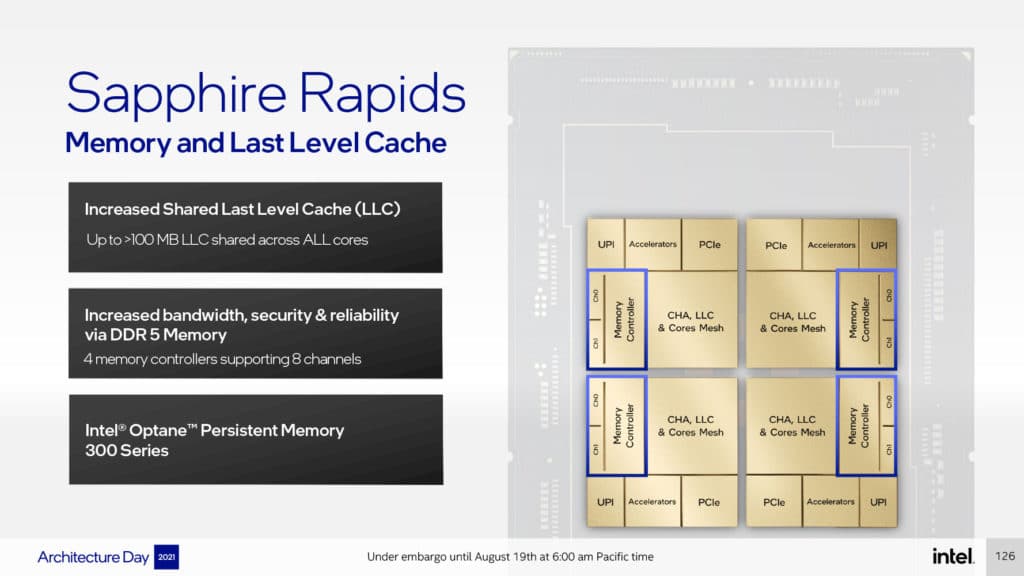

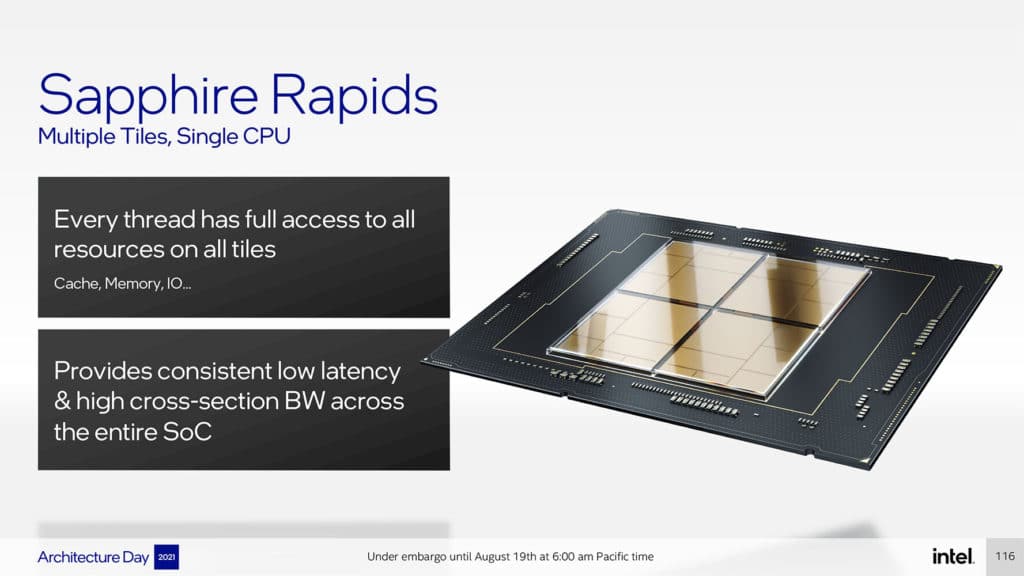

Intel a également révélé quelques informations concernant ses futurs processeurs Xeon Sapphire Rapids, lesquels succéderont aux Ice Lake-SP. Comme explicité sur l’une des diapositives, ils abandonnent une conception dite monolithique au profit d’une architecture multi-modules, à base de quatre “tiles”.

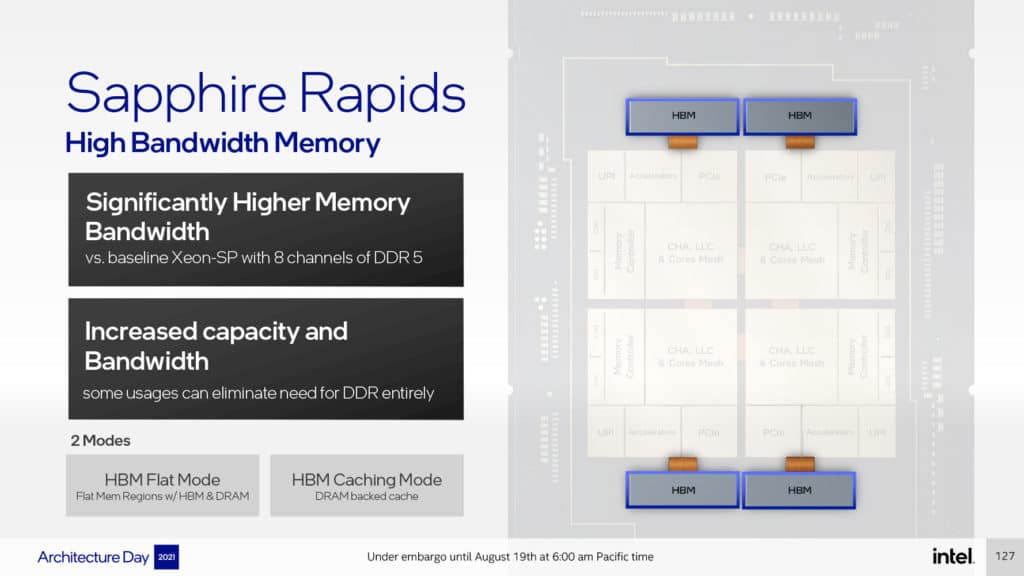

Chaque tile profite d’une interface mémoire DDR5 à deux canaux. Intel met également en avant l’accès d’une tile à la mémoire, au cache de dernier niveau et aux E/S d’une autre tile grâce à une interconnexion assurée par une interconnexion UPI 2.0 à 24 liens par tile pour une vitesse de transfert de 16 GT/s. Par ailleurs, comme le mentionnait des fuites, Intel équipera bien certaines puces Xeon Sapphire Rappids de mémoire HBM intégrée.

Source : Intel