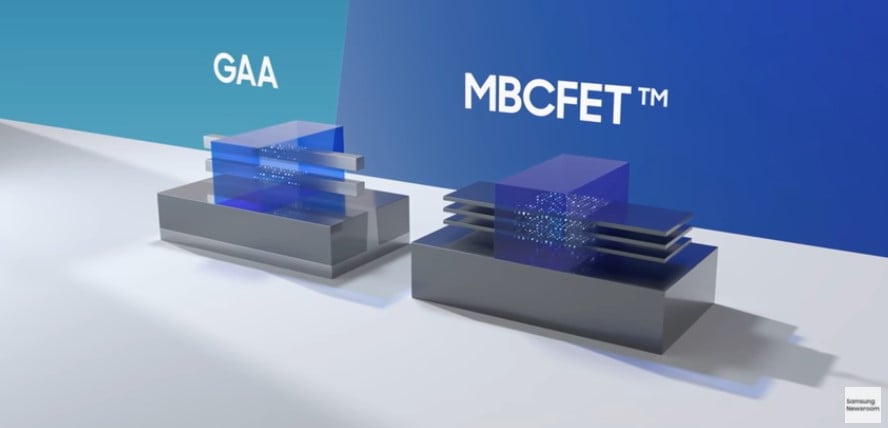

Le fondeur coréen amorce la transition vers des transistors GAA.

À l’occasion du Samsung Foundry Forum 2021, l’entreprise coréenne a dévoilé sa feuille de route concernant ses procédés de fabrication en 3 nm et 2 nm. Pour faire court, la société prévoit des premières puces en 3 nm dès l’année prochaine et en 2 nm d’ici quatre ans, soit en 2025.

Détaillé en mars dernier, le 3 nm de Samsung implique des transistors GAA (Gate-All-Around) de type MBCFET (Multi-Bridge Channel Field-Effect Transistor). Ce procédé 3GAE promet, par rapport au 7 nm FinFET, une hausse des performances de 30 % (à puissance et complexité égales), une consommation diminuée de 50 % (à fréquences et complexité égales), une réduction de la surface de 45 %. Les premières puces en 3 nm débarqueront dans le courant du premier semestre 2022. L’hypothèse d’un report de plusieurs mois évoquée par SemiAnalysis fin juin semble donc infirmée. En outre, une seconde génération du procédé 3 nm arrivera dans le courant de l’année 2023.

IBM dévoile le premier wafer gravé en 2 nm

Du 2 nm en 2025

Concernant le 2 nm, Samsung a communiqué peu d’informations. Nous savons uniquement que le procédé mobilisera toujours des transistors GAA MBCFET et que la firme prévoit une production de masse à partir du second semestre 2025 ; cette échéance impliquerait une commercialisation de premiers produits en 2 nm début 2026 au plus tôt. Samsung n’a pas dévoilé les gains fonctionnels qu’apportera technologie de fabrication.

Dr Siyoung Choi, président et chef de l’activité fonderie chez Samsung Electronics, a expliqué que le 2 nm “représenterait la troisième génération” de procédés de gravure utilisant les transistors GAA. En conséquence, il estime “que la transition de l’industrie vers le 2 nm se fera en douceur grâce à l’expérience acquise avec le 3 nm”.

Du côté de la concurrence, TSMC continuera d’employer des transistors FinFET pour ses procédés N4 et N3. Le fondeur taïwanais ne prévoit de passer à des transistors GAA qu’à partir du 2 nm.

Chez Intel, les nœuds Intel 7, 4 et 3, qui correspondent à du 10 nm dans le premier cas et à du 7 nm dans les deux autres, reposent eux aussi sur des FinFET. Les transistors GAA ne seront introduits qu’en 2024, si tout se passe bien, par l’intermédiaire des RibbonFET (la terminologie utilisée par Intel) de l’Intel 20A (pour 20 ångströms, soit du 2 nm).

Source : Samsung

On ne peut pas prédire la sortie de ses processus de gravure, c’est trop loin.On l’a vu plusieurs fois depuis des années, il y a tellement d’imprévu possible et surtout avec la crise actuelle qu’on a beaucoup de chance que ses plannings soit reportés de plusieurs années. Intel devait passé au 10 mn y a bien longtemps et finalement, celui y passe seulement maintenant sur les professeurs de bureau, Intel était pourtant leader de la gravure et en avance depuis longtemps, celui ci s’est fait rattraper et dépasser depuis et se retrouve en retard même si ses gravures réelles sont beaucoup plus fines que ses appellations. D’ailleurs il devrait y avoir une loi pour encadrer les appellations, aujourd’hui c’est n’importe quoi.

Donc on verra déjà si le développement si le développement des gravures moins fines comme les 5 nm et 3 nm ne posent pas de problème avant de s’occuper de plus fin.En tous cas si Intel s’aligne sur les appellations des autres ce serait une bonne nouvelle pour pouvoir mieux comparer les gravures et architectures.Mais d’après les dernières informations, Samsung est partie pour être en retard et moins performant que les tmsc et Intel en terme de densité sur ses gravures en 2025, rendez vous en 2025 pour voir ou en seront tout ce petit monde…