Un socket LGA-4844 pour des serveurs plus compacts, avec des spécifications inférieures à celles de la plateforme SP5.

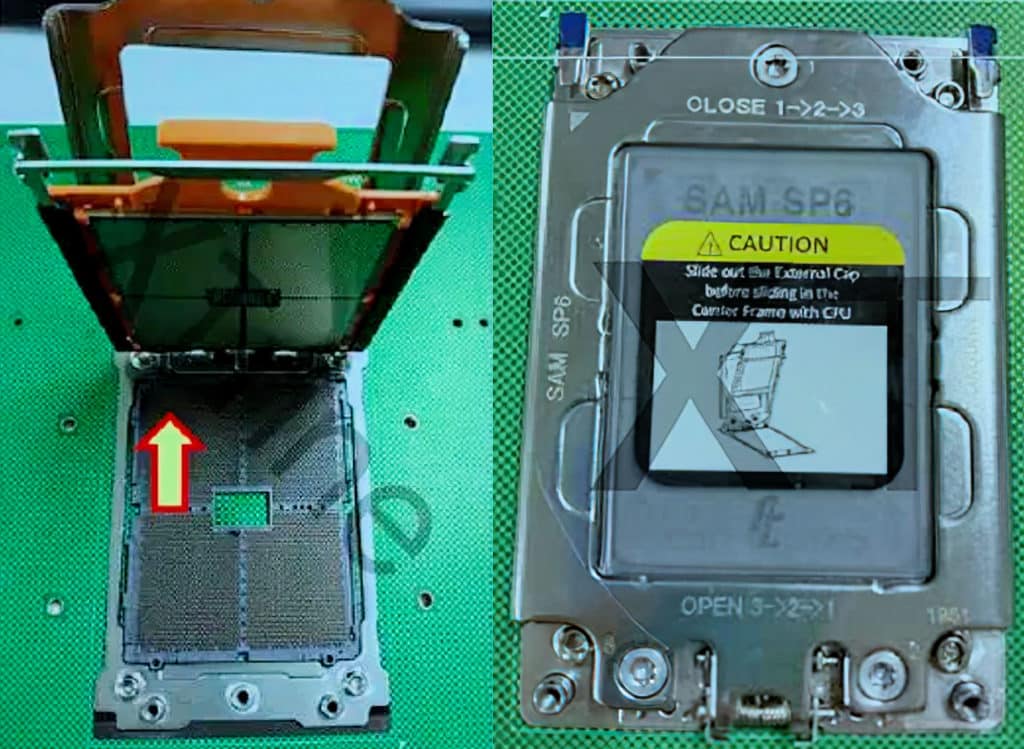

La prochaine série de processeurs EPYC, EPYC 7004 “Genoa” et “Bergamo”, passera à l’architecture CPU Zen 4 et à une gravure en 5 nm ; cette génération offrira 50 % de cœurs CPU en plus en passant de 64 à 96 au mieux. Côté socket, elle marquera l’abandon du SP3 (LGA-4094) et le passage au SP5 (LGA-6096). Ce socket SP5 pourrait cohabiter avec un autre socket, le SP6 (LGA-4844). Des clichés ont été publiés sur les forums d’AnandTech.

L’intérêt de mobiliser deux sockets ? Diversifier les plateformes. Le socket SP6 servirait pour des serveurs plus compacts. Une telle segmentation est déjà employée par Intel. La firme propose des processeurs Xeon Scalable mais également des Xeon D qui “offrent des performances optimisées pour les charges de travail dans les environnements contraints en termes d’espace et d’alimentation, du centre de données à la périphérie intelligente du réseau”. Les processeurs Intel Xeon Platinum par exemple prennent place sur un socket FCLGA4189 dans un conditionnement de 77,5 x 56,5 mm ; les Xeon D sur un socket FCBGA2227 avec un conditionnement de 45 x 45 mm.

Pour les plateformes AMD, les spécifications seraient les suivantes :

| Socket | Broches | Dimensions | Nombre max de cœurs | Max TDP |

| SP3 | LGA 4094 | 58,5 x 75,4 mm | Zen 3 : 64 | 280W |

| SP5 | LGA 6096 | 76,0 x 80,0 mm | Zen 4 : 96 / Zen 4c : 128 | 400W |

| SP6 | LGA 4844 | 58,5 x 75,4 mm | Zen 4 : 32 / Zen 4c: 64 | 225W |

La série EPYC 7006 aurait pour nom de code “Venice”

AMD EPYC Genoa et Bergamo

Le socket SP5 à 6096 broches devrait gérer les processeurs EPYC 7004 ayant jusqu’à 96 cœurs Zen 4 ou 128 cœurs Zen 4c, et des TDP max de 400 W. Le socket SP6 à 4844 broches supporterait des processeurs ayant des TDP de 225 W max. Il y aurait aussi quelques disparités au niveau du nombre de lignes PCIe 5.0 supportées : 160 pour le SP5, 96 pour le SP6.

| Série | 3e génération EPYC « Milan / Milan-X (*) » | 4e génération EPYC « Genoa / Genoa-X (*) » | 4e génération EPYC « Bergamo » | 5e génération EPYC « Turin » |

| Lancement | 2021 | 2022 ? | 2022 ? | 2023/2024 ? |

| Architecture | 7nm Zen3 | 5nm Zen4 | 5nm Zen4c | Zen5 |

| Socket | SP3 (LGA4094) | SP5 (LGA-6096) SP6 (LGA-4844) | SP5 (LGA-6096) SP6 (LGA-4844) | SP5 (LGA-6096) SP6 (LGA-4844) |

| Modules/Chiplets | 8xCCD + 1xIOD | 12xCCD + 1xIOD | À déterminer | À déterminer |

| Nombre max de cœurs | 64C / 128T | 96C / 192T | 128C / 256T | 256C / 512T |

| Cache L2 par cœur | 0,5 Mo | 1 Mo | À déterminer | À déterminer |

| Cache L3 par CCX | 32 Mo / 96 Mo (*) | 32 Mo / ?? Mo (*) | À déterminer | À déterminer |

| Support mémoire | 8-canaux | 12-canaux (SP5) 6-canaux (SP6) | 12-canaux (SP5) 6-canaux (SP6) | 12-canaux (SP5) 6-canaux (SP6) |

| Type mémoire | DDR4-3200 | DDR5-5200 | DDR5-5200 | DDR5-6000 |

| Lignes PCIe | 128x Gen4 | 160x Gen5 (SP5) 96x Gen5 (SP6) | 160x Gen5 (SP5) 96x Gen5 (SP6) | À déterminer |

| Max cTDP | 280W | 200-400W (SP5) 70-225W (SP6) | 200-400W (SP5) 70-225W (SP6) | À déterminer |

Sources : AnandTech via Tom’s Hardware US / VideoCardz

mouais ou alors le SP6 est le socket pour les futurs TR… est il supportera probablement 64c ZEN4 comme les TR et EPYC actuels…