Des puces qui chauffent moins, consomment moins d’énergie et proposent des performances nettement meilleures, vous en rêvez ? C’est pour l’année prochaine !

Le fabricant taïwanais TSMC a récemment dévoilé de nouveaux détails sur son processus de gravure en 2 nm lors de la conférence IEEE International Electron Device Meeting (IEDM) à San Francisco. Cette technologie, baptisée “N2 nanosheet”, marque une étape majeure dans l’évolution des semi-conducteurs grâce à des améliorations significatives en performance, efficacité énergétique et densité des transistors.

Améliorations notables du processus N2

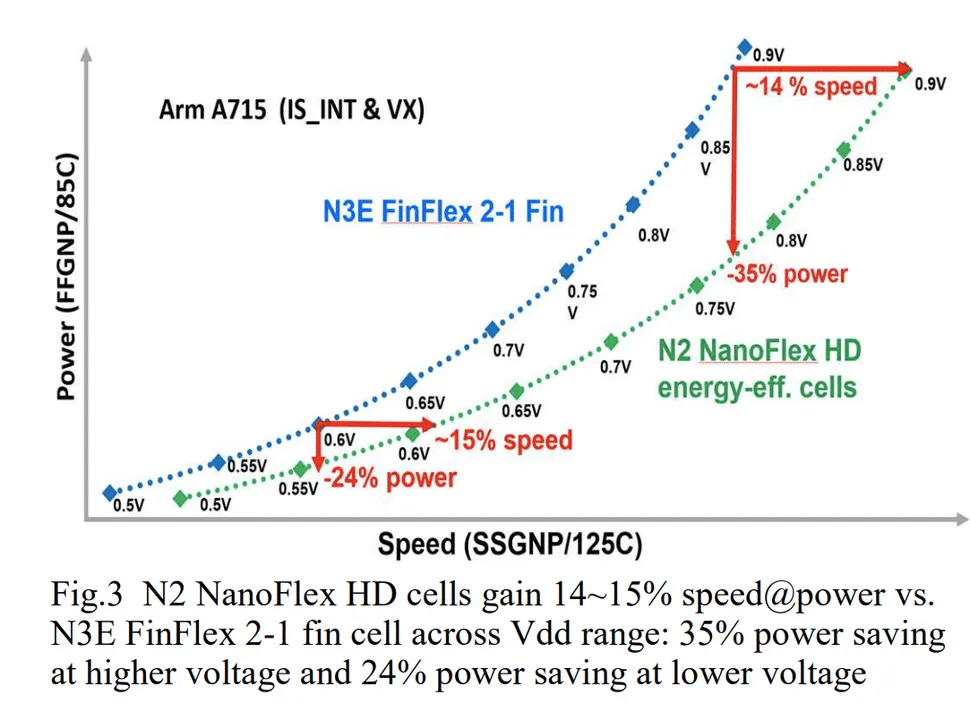

Selon TSMC, le processus 2 nm devrait apporter :

- Une augmentation de 15 % des performances par rapport au processus en 3 nm.

- Une réduction de 30 % de la consommation énergétique, permettant des puces plus économes en énergie.

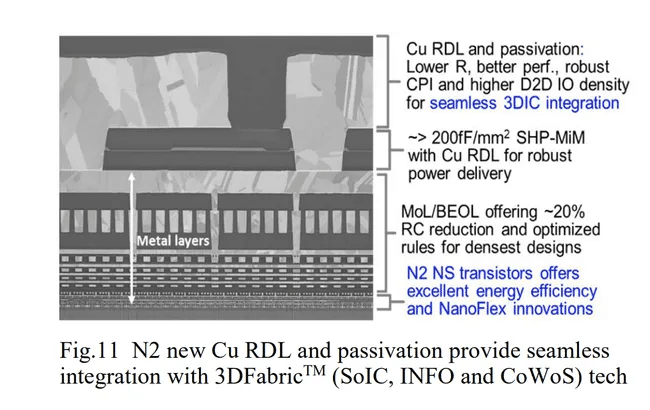

- Une densité de transistors augmentée de 15 %, grâce à l’adoption des transistors GAA (Gate-All-Around) basés sur des nanosheets et à l’utilisation de la technologie N2 NanoFlex, qui optimise l’intégration des cellules logiques sur la surface de la puce.

Le passage de la technologie traditionnelle FinFET aux nanosheets permet un contrôle plus précis du flux de courant grâce à des rubans de silicium entourés par des grilles. Cette innovation offre une flexibilité accrue pour adapter les paramètres en fonction des cas d’utilisation, un avantage crucial pour les fabricants.

Des puces rapidement adoptées mais onéreuses

La production de masse de ces puces est prévue pour le second semestre 2025. Ce processus devrait connaître une adoption rapide par des entreprises majeures telles qu’Apple et Nvidia, en raison des avancées qu’il apporte par rapport aux technologies de gravure précédentes. Cependant, les premiers taux de rendement et les coûts élevés pourraient freiner une adoption immédiate à grande échelle.

Le processus en 2 nm s’accompagne d’une augmentation des coûts. TSMC estime que le prix d’une plaque de silicium (wafer) gravée en 2 nm se situera entre 25 000 et 30 000 dollars, contre environ 20 000 dollars pour le 3 nm. Cette hausse de coût pourrait se traduire par une montée des prix pour les produits finaux, notamment les processeurs et autres composants utilisant cette technologie.

Des puces toujours plus performantes

Avec le N2, TSMC franchit une nouvelle étape dans la miniaturisation et l’optimisation des semi-conducteurs, répondant aux besoins croissants en puissance de calcul et en efficacité énergétique des secteurs technologiques. Bien que des éléments à considérer ne fassent pas de ce nouveau processus un long fleuve tranquille, des éléments notamment financiers, cette avancée renforce la position de TSMC en tant que leader dans le domaine des semi-conducteurs avancés.