L’Universal Chiplet Interconnect Express : un standard pour les interconnexions die-to-die.

Plusieurs poids lourds du secteur annoncent la création d’un consortium UCIe (Universal Chiplet Interconnect Express). Il a pour but de “normaliser les interconnexions die-to-die”, autrement dit définir une interconnexion standardisée entre différents chiplets. Le communiqué stipule que cette norme établit “une interconnexion universelle au niveau du package” et invite “les entreprises et institutions intéressées à s’y joindre”.

Les entreprises à l’origine de cette initiative sont Advanced Semiconductor Engineering, Inc. (ASE), AMD, Arm, Google Cloud, Intel Corporation, Meta, Microsoft Corporation, Qualcomm Incorporated, Samsung et Taiwan Semiconductor Manufacturing Company (TSMC). Les trois principaux fondeurs sont donc de la partie, et le consortium englobe les écosystèmes x86 et ARM. En revanche, vous l’aurez constaté, un grand absent se fait remarquer dans cette liste : NVIDIA. L’architecture RISC-V semble également écartée du projet à ce stade.

Diapo : tous les processeurs d’AMD en 36 ans d’histoire

Vers un marché des chiplets

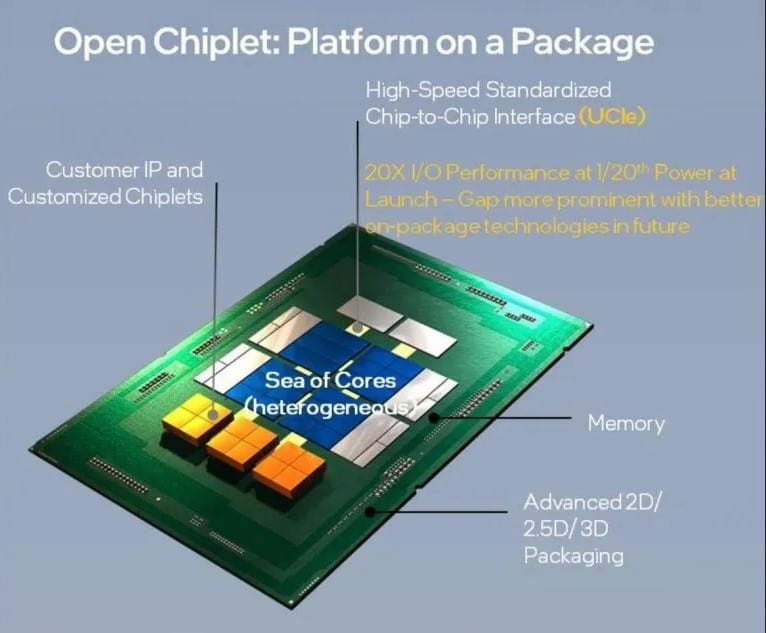

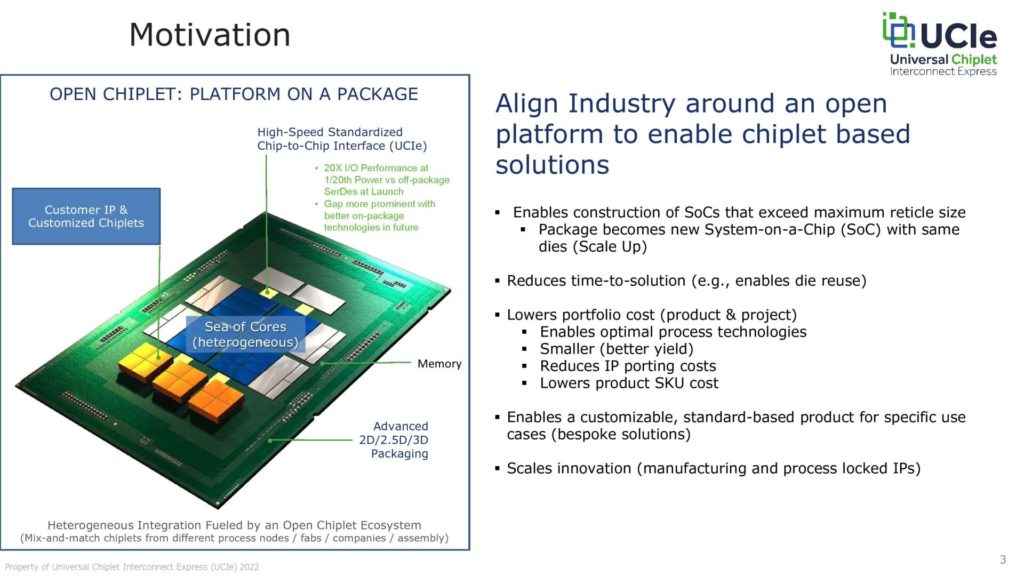

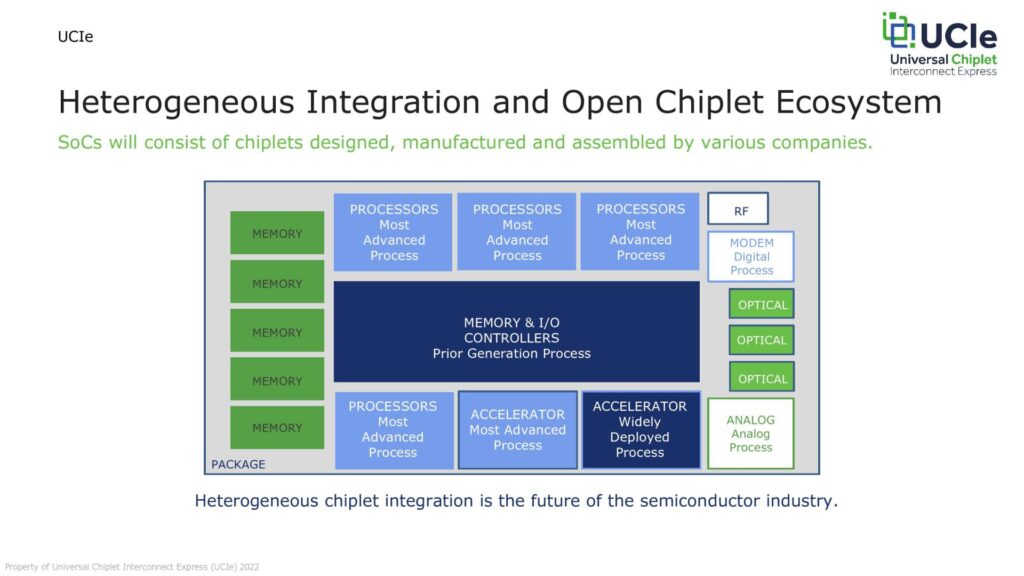

À l’inverse d’une conception dite monolithique, le principe des chiplets consiste à combiner et interconnecter différents modules, les chiplets, qui disposent de leur propre die, au sein d’un même package. C’est un assemblage en mode “Lego” en quelque sorte. Les chiplets peuvent être fabriqués à partir de nœuds de gravure différents. AMD a recours aux chiplets pour ses processeurs depuis le l’architecture Zen 2, soit les Ryzen 3000. Pour les GPU, les accélérateurs AMD Instinct Series MI200 profitent également d’une conception MCM (multi-chip module).

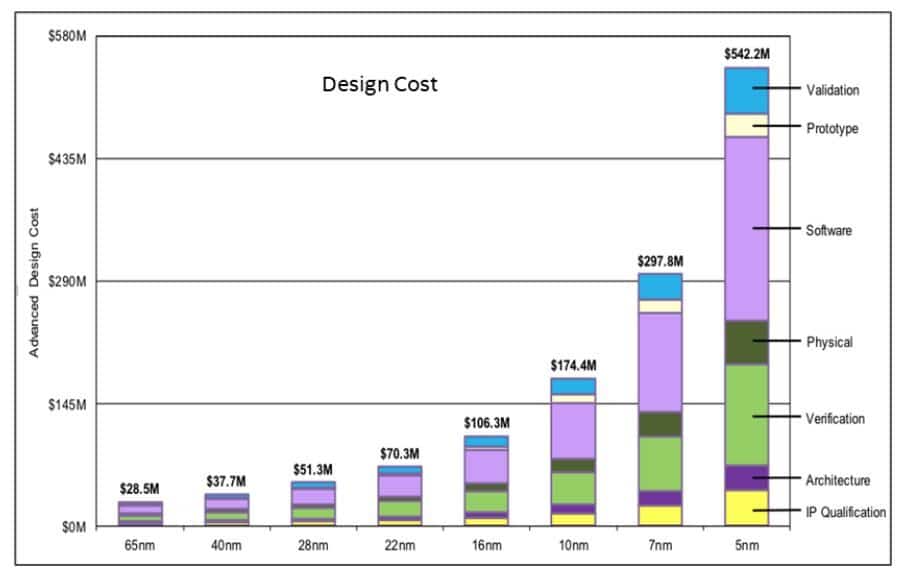

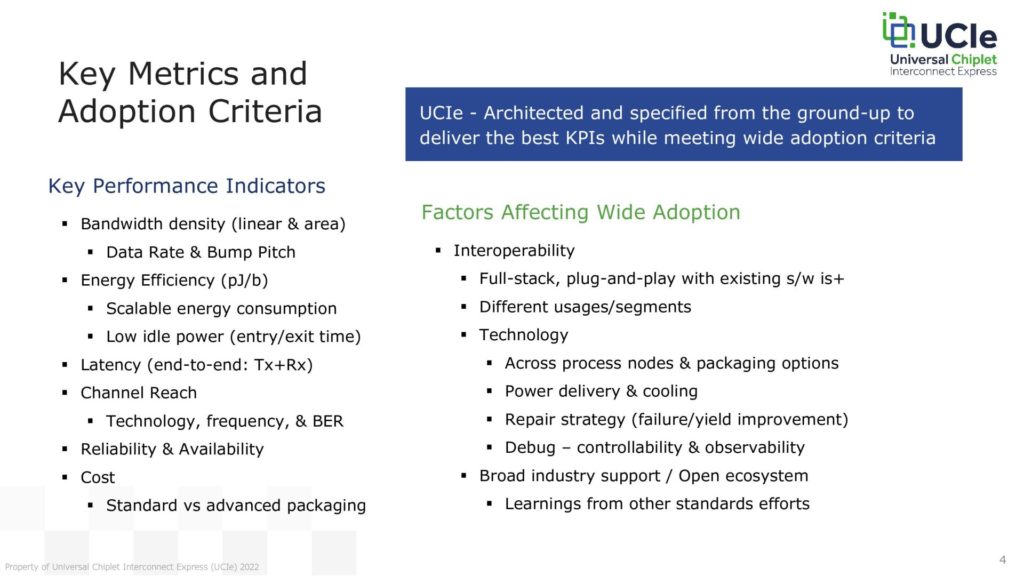

À terme, dans une optique de réduction des coûts et d’amélioration des performances, un marché de modules (chiplets) “prêts à l’emploi” est tout à fait envisageable. Seulement pour qu’une telle pratique soit viable, il faut que l’interconnexion entre les chiplets soit standardisée, à la manière des différents protocoles que mobilise une carte mère par exemple. C’est ce que veut faire l’UCIe.

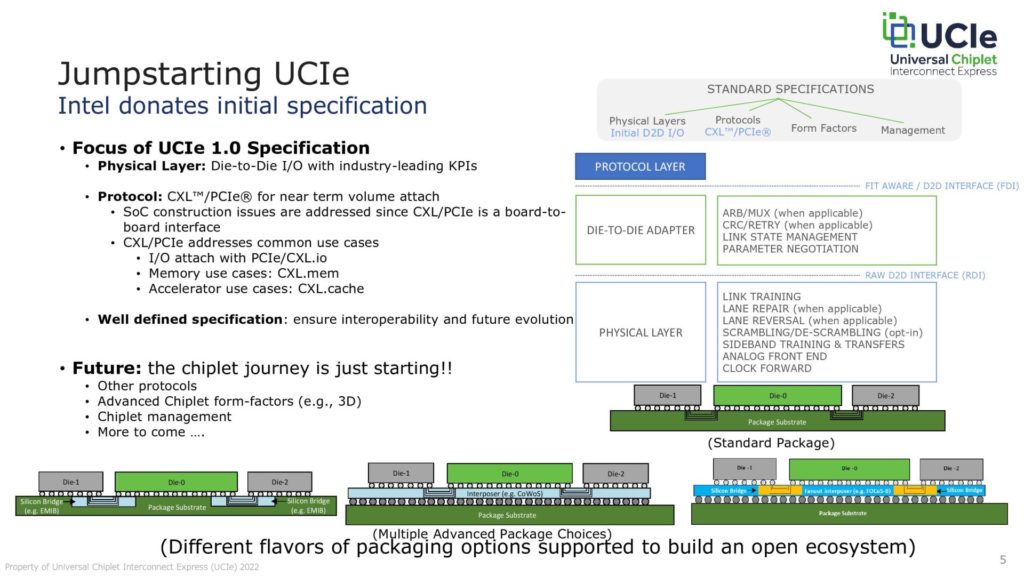

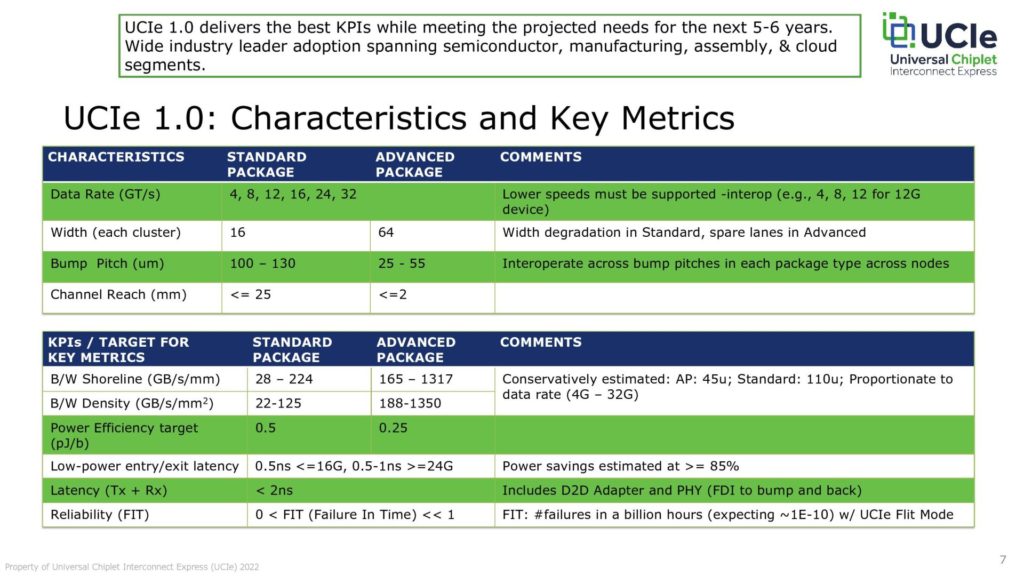

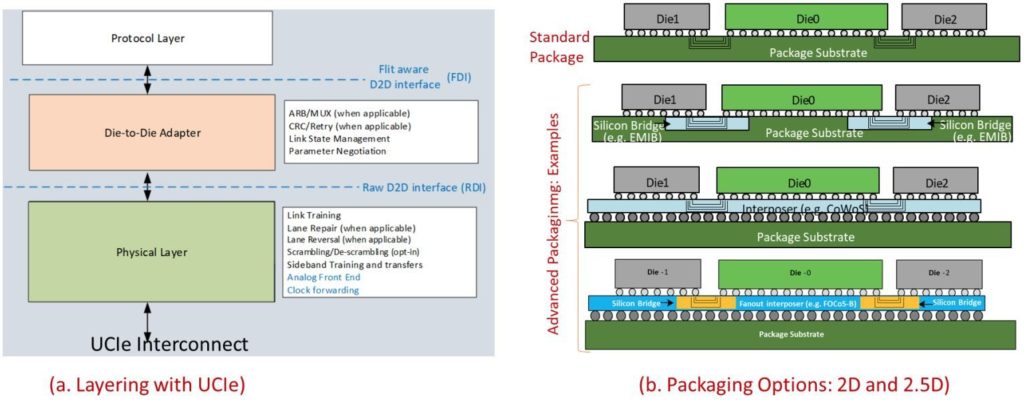

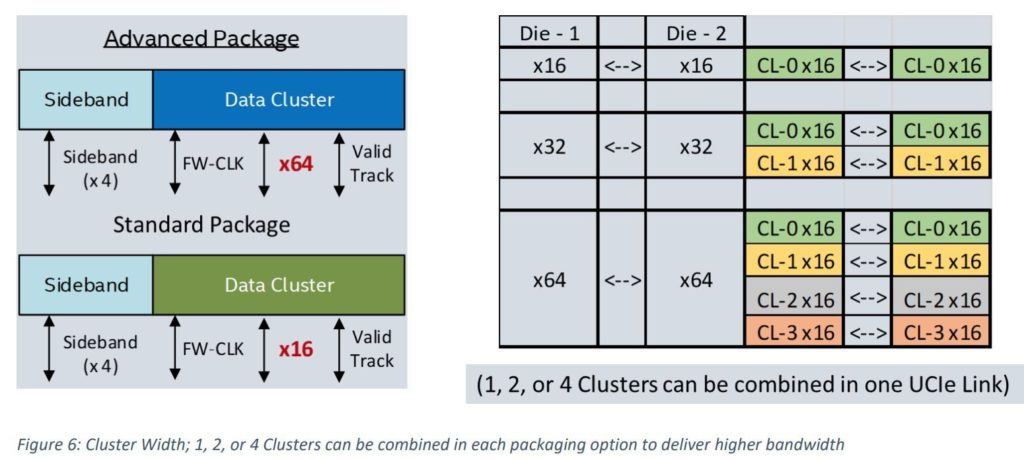

Le consortium divise les objectifs en deux grandes catégories : les techniques de conditionnement 2D standard et les techniques 2,5D plus avancées (EMIB d’Intel, CoWoS de TSMC…).

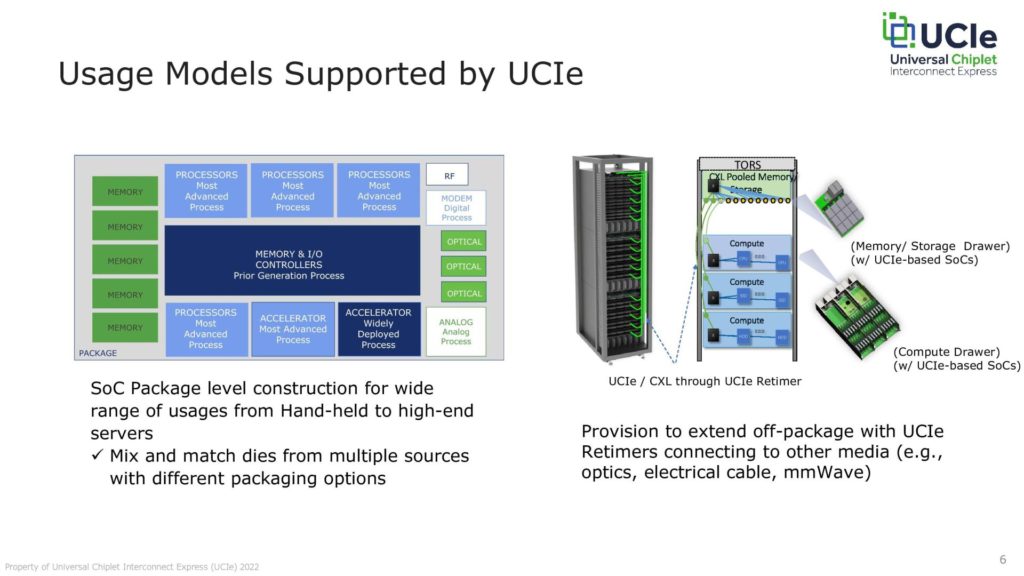

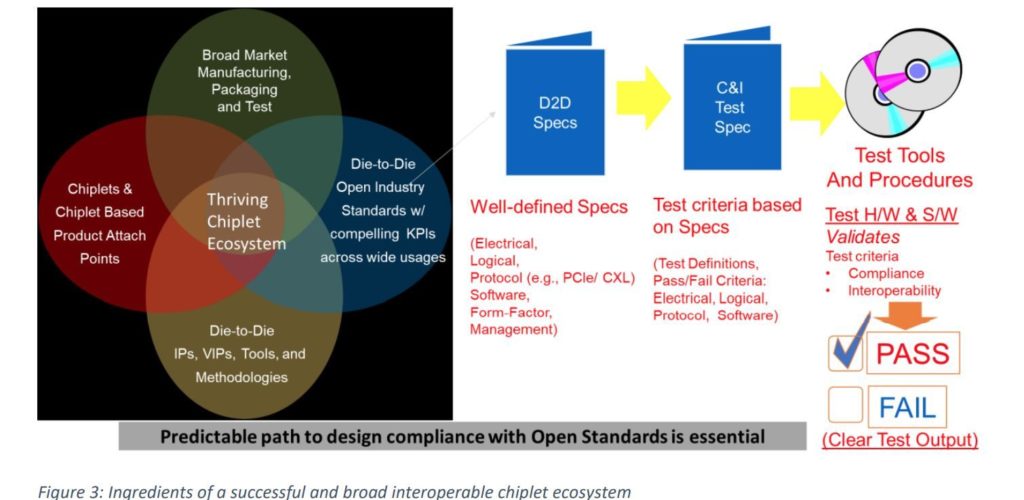

Selon les diapositives, le protocole s’exécute au-dessus de la couche physique, soit en PCIe soit en CXL (Compute eXpress Link). Le protocole PCIe offre une interopérabilité et une flexibilité maximales, tandis que le protocole CXL se concentre sur des connexions à faible latence et à haut débit. La spécification UCIe 1.0 se borne aux PCIe et CXL mais d’autres protocoles seront intégrés à l’avenir.

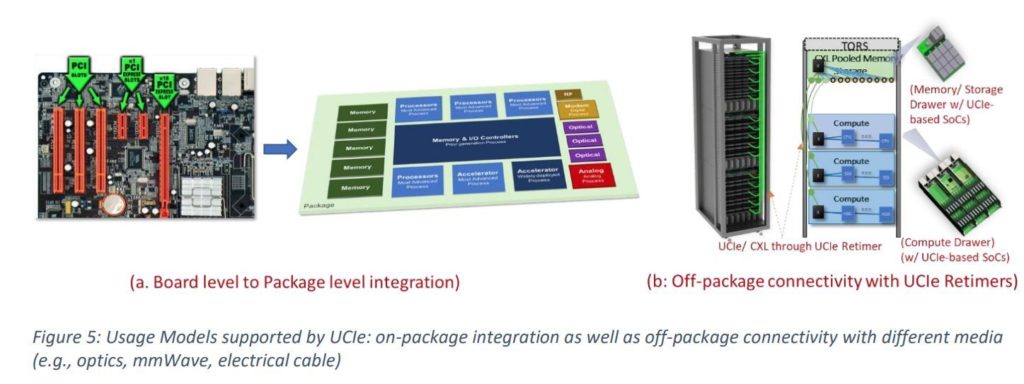

Par ailleurs, le consortium UCIe ambitionne aussi de proposer une interconnexion à plus grande échelle, bien au-delà du package d’une puce : jusqu’à celle du rack serveur.

La spécification UCIe 1.0 est disponible dès à présent. Vous pouvez consulter toutes les informations sur le site web officiel du consortium UCIe.