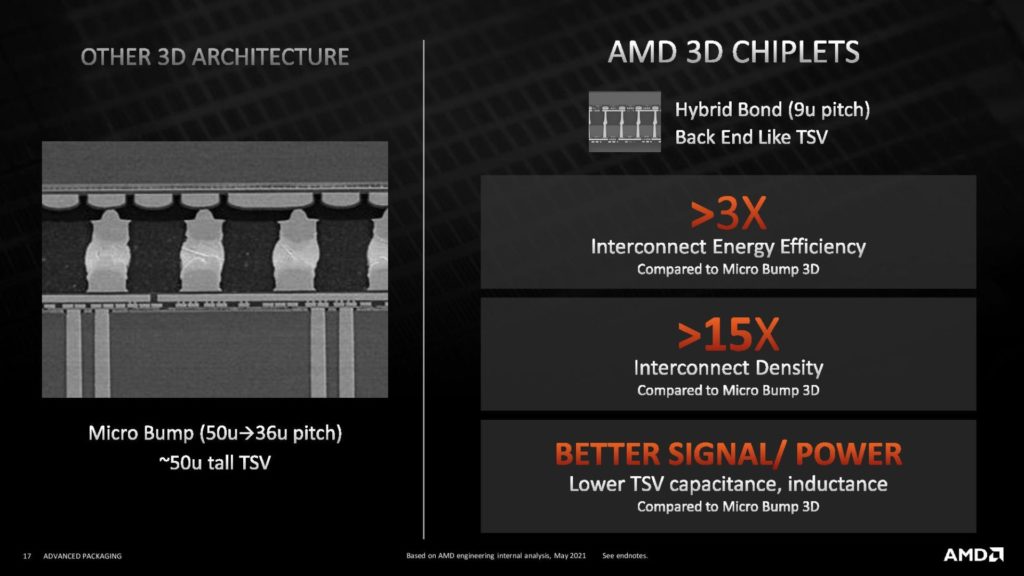

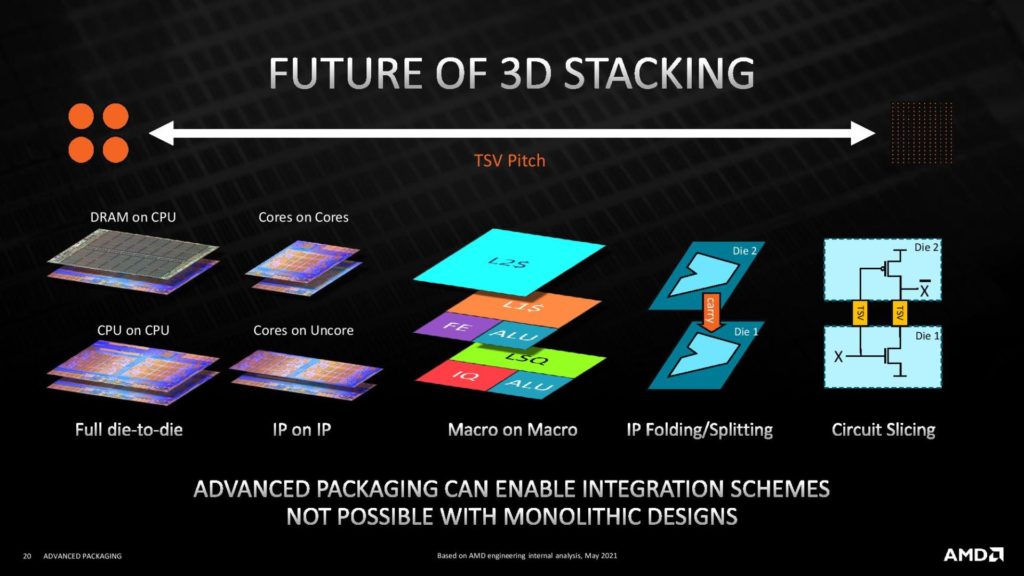

Des interconnexions TSV offrant une efficacité énergétique 3 fois plus élevée et une densité 15 fois supérieure à celles des micro-bosses 3D.

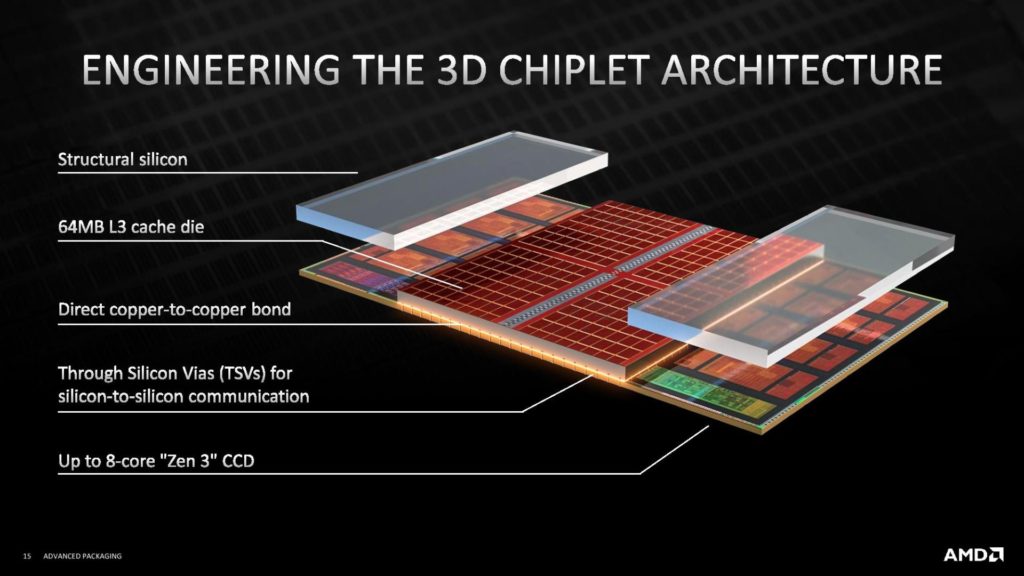

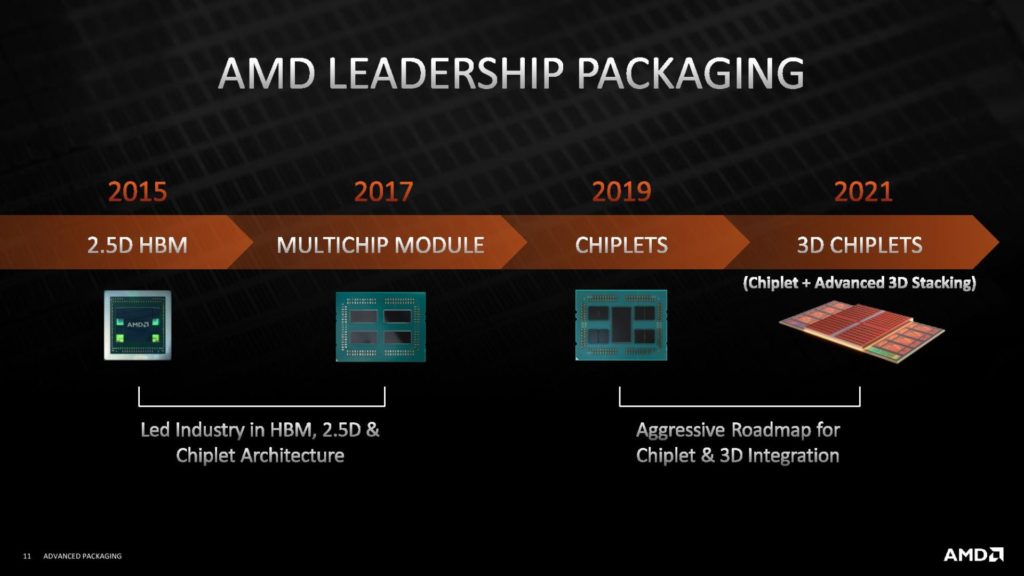

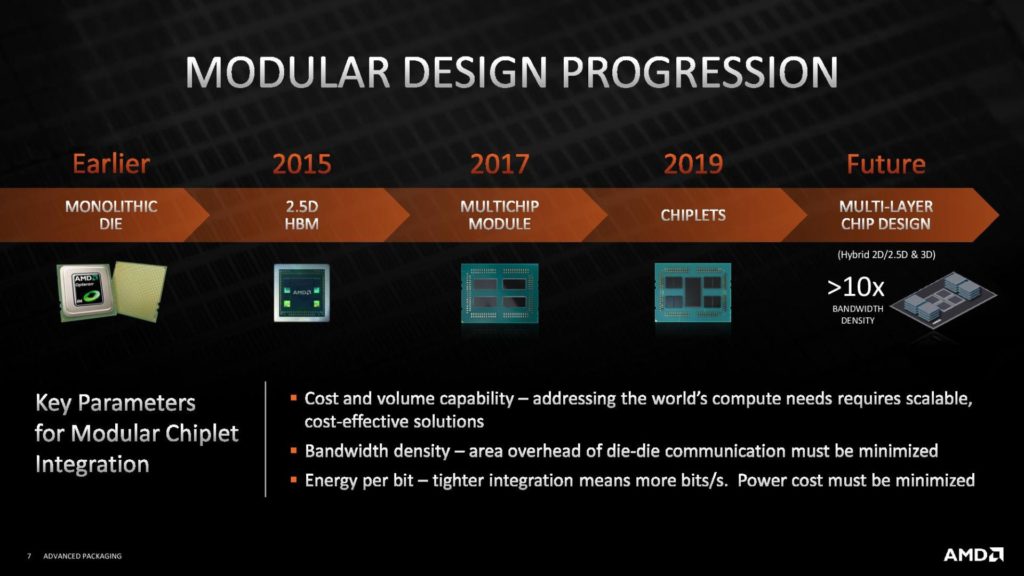

AMD a profité de la Hot Chips 33 pour détailler sa technologie 3D Chiplet. L’entreprise avait illustré ce procédé d’empilement 3D, présenté pour la première fois lors du Computex 2021, par l’ajout d’un cache L3 vertical à un processeur Ryzen, au-dessus de ses CCD. En l’état, il est possible d’empiler 64 Mo de cache L3 par CCD, soit 128 Mo. Au total, cela permet de tripler la quantité de cache L3 en ouvrant la voie à des processeurs armés de 192 Mo de cache L3, contre 64 Mo actuellement.

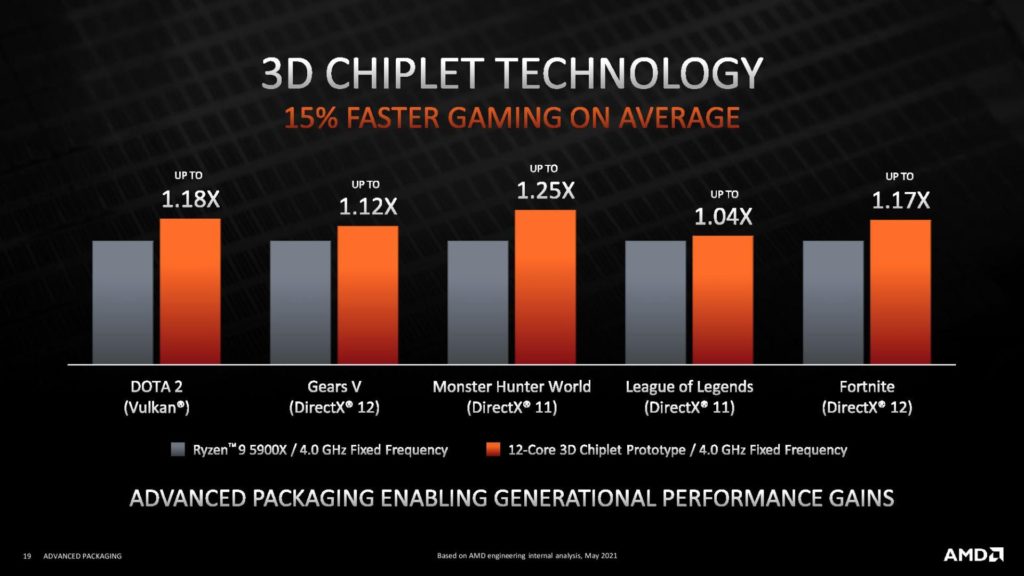

Selon AMD, ce cache L3 supplémentaire accorde un boost de performances non négligeable de 15 % en moyenne dans les jeux pour un Ryzen 9 5900X. C’est d’autant plus remarquable que ce gain ne résulte ni d’un changement de gravure ni d’un changement d’architecture CPU : le prototype est toujours une puce Zen 3 gravée en 7 nm.

Débit entre les deux dies de 2 To/s

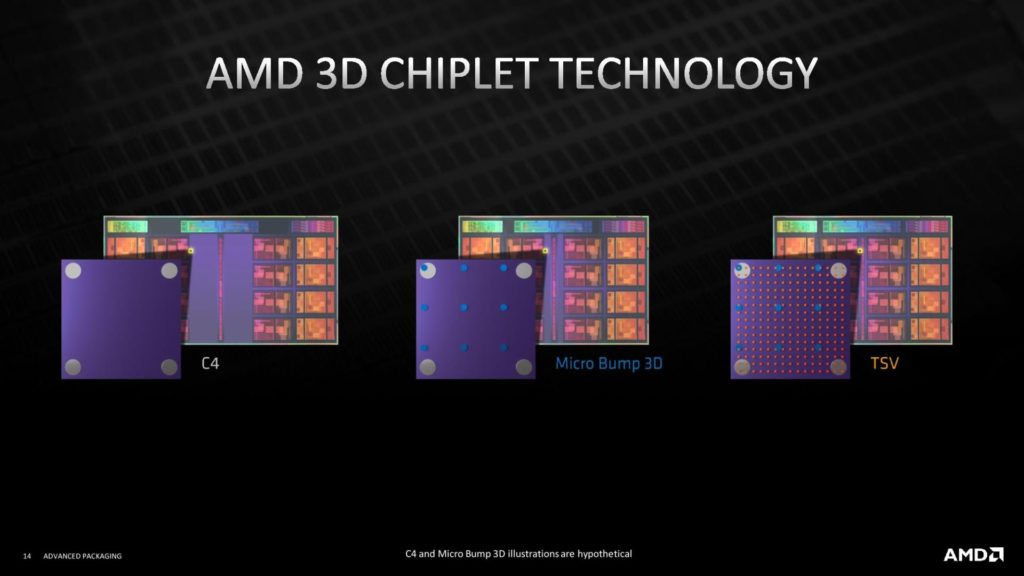

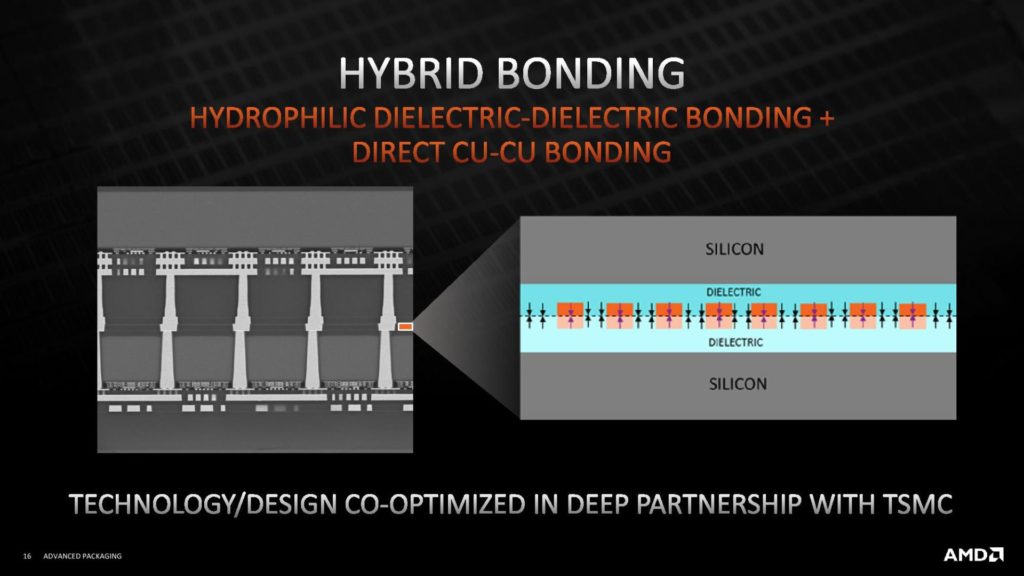

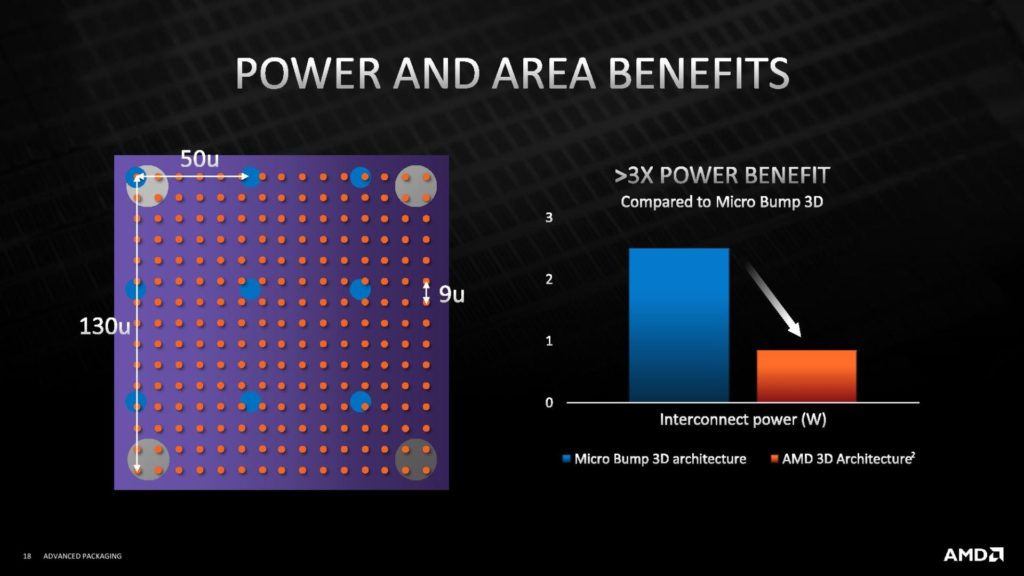

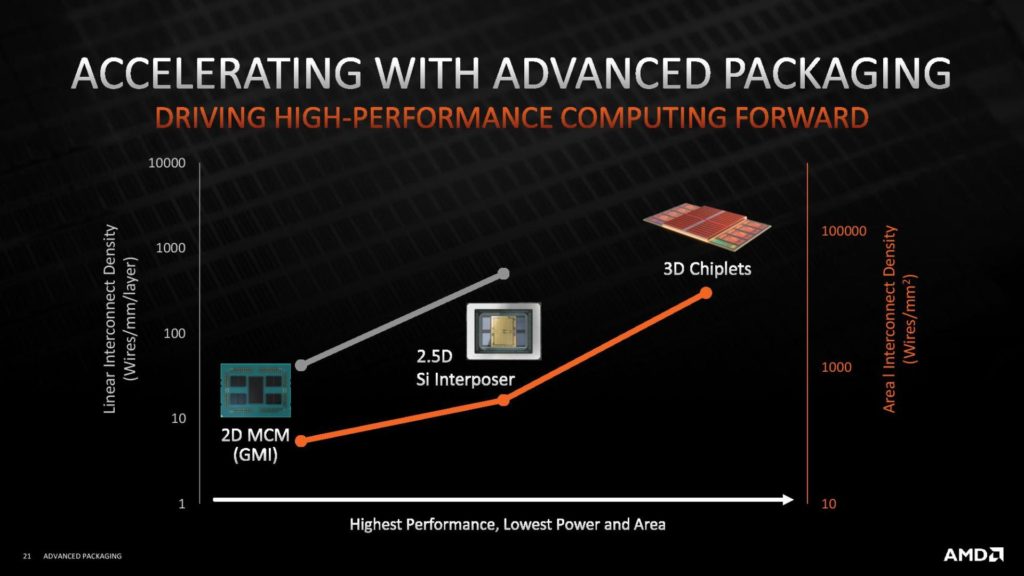

Comme AMD l’avait évoqué en juin dernier dans une vidéo, pour ajouter ce cache vertical, l’entreprise fait appel au procédé SoIC de TSMC : il consiste à relier la puce SRAM avec le die par l’intermédiaire d’une liaison diélectrique directe cuivre-cuivre grâce aux TSV (Through Silicon Vias). Par rapport à une technique d’interconnexion via micro-bosses, cette méthode s’avère trois fois plus efficace en matière de consommation et offre une densité 15 fois supérieure ; selon d’autres informations communiquées par Yuzo Fukuzaki, il y aurait 23 000 TSV de 17 µm. D’autre part, le débit entre les deux dies est de 2 To/s ; l’impact sur la latence est minime selon AMD.

Une diapositive met en avant un espacement de seulement 9 μm (micromètres) entre les TSV. Pour la comparaison, cet écart est de 50 μm pour des micro-bosses 3D, de 55 μm pour l’EMIB de première génération, 45 μm pour l’EMIB de seconde génération ; 36 μm pour l’EMIB de troisième génération ; Intel évoque toutefois 10 μm pour son Foveros Direct prévue fin 2023.

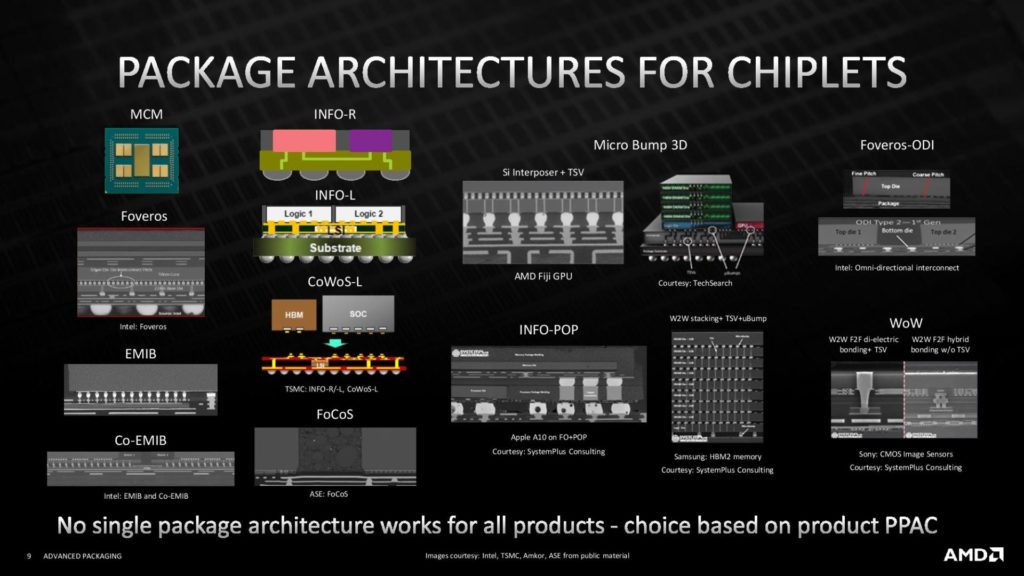

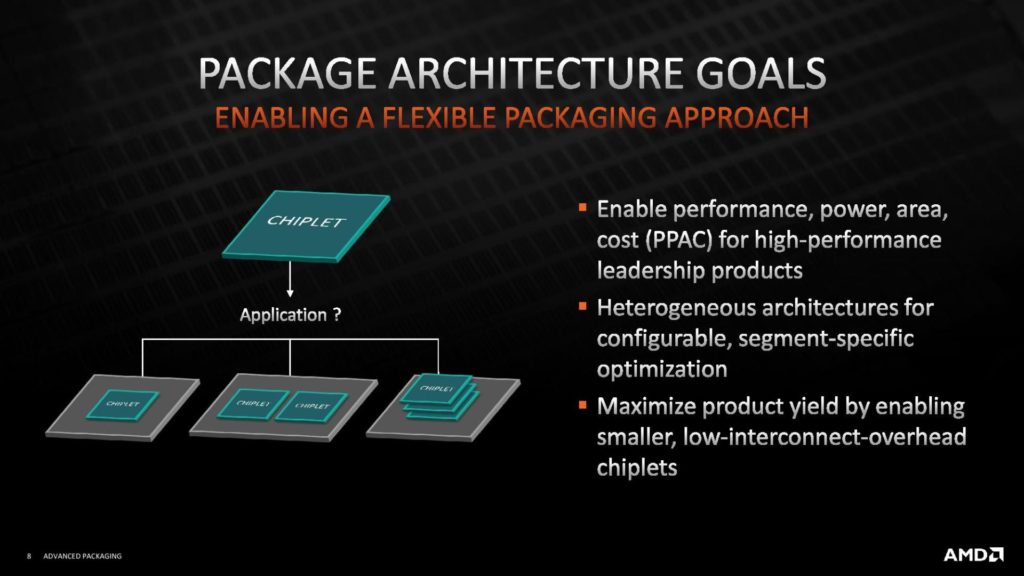

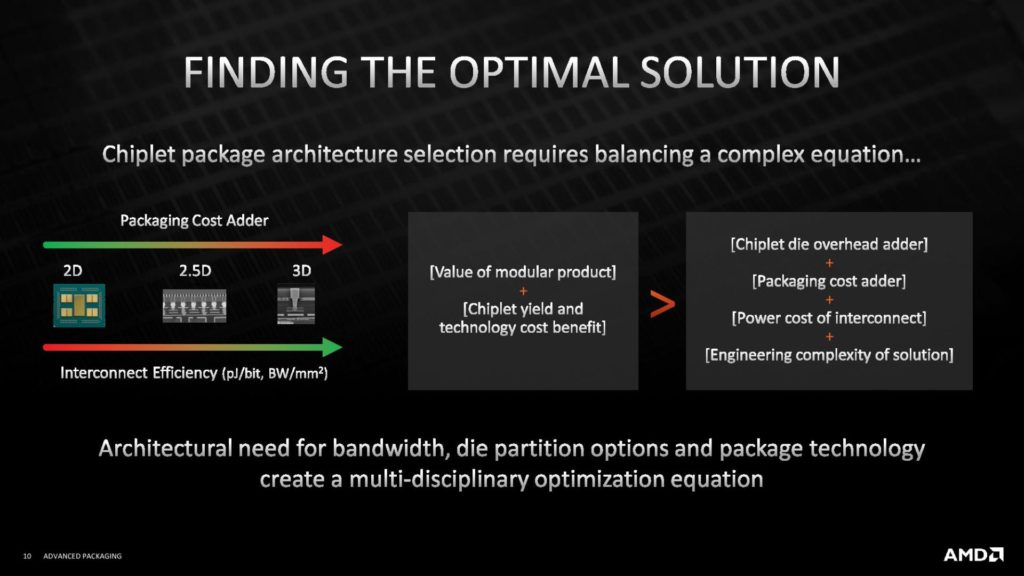

Quoi qu’il en soit, comme le stipule l’une des diapositives ci-dessous, aucune technologie de packaging n’est la panacée. AMD pourrait lancer une gamme de Ryzen 5000 Refresh affublés de ce fameux 3D V-Cache en début d’année prochaine.

Sources : Tom’s Hardware US, AnandTech