Des puces sous architecture CPU Zen 4 gravées en 5 nm qui prendraient en charge 128 lignes PCIe 5.0 et 12 canaux de DDR5-5200.

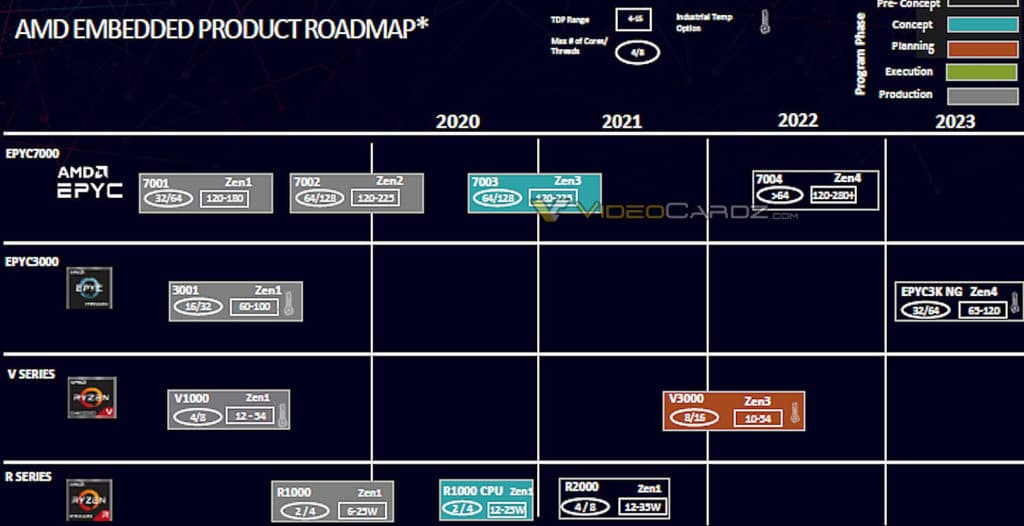

AMD a lancé ses processeurs pour serveurs EPYC 7003, nom de code EPYC Milan, en mars dernier. Par rapport à la précédente génération, EPYC Rome, les puces EPYC Milan bénéficient de l’architecture CPU Zen 3 qui booste les IPC ; pour le reste, elles ont conservé la plupart des caractéristiques de leurs ancêtres directs, notamment en ce qui concerne le nombre de cœurs maximal (64 cœurs) et la quantité de lignes PCIe et canaux mémoire pris en charge (128 lignes PCIe 4.0 et 8 canaux de DDR4-3200). La prochaine génération, EPYC 7004, alias EPYC Genoa, marquera une progression plus importante.

En effet, les processeurs EYPC Genoa profiteront d’une architecture CPU Zen 4, synonyme d’un nœud de gravure en 5 nm. Une nouvelle diapositive type feuille de route confirme un nombre maximal de cœurs CPU plus élevé : certainement jusqu’à 96 cœurs / 192 threads grâce une conception passant de 8 à 12 chiplets. Cette hausse aura des répercussions sur le TDP, susceptible d’atteindre 320 W pour certaines puces. Par ailleurs, selon VideoCardz, ces processeurs EPYC Genoa prendraient en charge 128 lignes PCIe 5.0 et la mémoire DDR5-5200 sur 12 canaux.

AMD adopterait une conception de type big.LITTLE pour ses Ryzen 8000

Gamme EPYC

Le tableau ci-dessous rassemble les caractéristiques des gammes EPYC d’AMD.

| Gamme EPYC | 7001 “Naples” | 7002 “Rome” | 7003 “Milan” | 7004 “Genoa” |

|---|---|---|---|---|

| Année de lancement | 2017 | 2019 | 2021 | 2022 |

| Architecture | 14nm Zen | 7nm Zen2 | 7nm Zen3 | 5nm Zen4 |

| Socket | SP3 (LGA4094) | SP3 (LGA4094) | SP3 (LGA4094) | SP5 (LGA-6096) |

| Modules/Chiplets | 4x CCD | 8x CCD + 1x I/0 | 8x CCD + 1x I/O | 12x CCD + 1x I/O |

| Nombre maximal de cœurs | 32C/64T | 64C/128T | 64C/128T | 96C/192T |

| Fréquence max | 3,8 GHz | 3,9 GHz | 4,1 GHz | TBC |

| Support mémoire | 8c DDR4-2666 ECC | 8c DDR4-3200 ECC | 8c DDR4-3200 EEC | 12c DDR5-5200 ECC |

| Lignes PCIe | 128x Gen3 | 128x Gen4 | 128x Gen4 | 128x Gen5 |

| TDP max | 200W | 280W | 280W | 320W |

Plus de cœurs également chez Intel

Chez Intel, les Xeon Scalable de 3e génération, Ice Lake-SP, ont débarqué en avril. Gravés non plus en 14 nm comme les Cascade Lake mais en 10 nm, ils ont fait passer le nombre maximal de cœurs de 28 à 40. En outre, ils gèrent 8 canaux de DDR4-3200 contre 6 canaux de DDR4-2933 et prennent en charge 64 lignes PCIe 4.0 contre 48 lignes PCIe 3.0 pour Cascade Lake.

Leurs successeurs, les Sapphire Rapids, géreraient la mémoire DDR5 et 80 lignes PCIe 5.0. Quant au nombre maximal de cœurs pour cette génération, il passerait à 56 voire 80.