Le Flash Memory Summit qui se tient actuellement à Santa Clara (Californie) donne lieu à un feu d’artifice d’annonces de la part des grands industriels du stockage. Toshiba a ouvert le feu avec ses puces de flash 3D BiCS TLC de 256 Gbit, suivies de l’annonce des premières puces utilisant des TSV pour empiler 16 dies. Samsung a répondu en présentant ses propres puces TLC V-NAND de 256 Gbit qui lui permettront de créer un SSD de 15,36 To ! Toshiba revient à la charge aujourd’hui en discutant de l’avenir : la mémoire QLC à 4 bits par cellule.

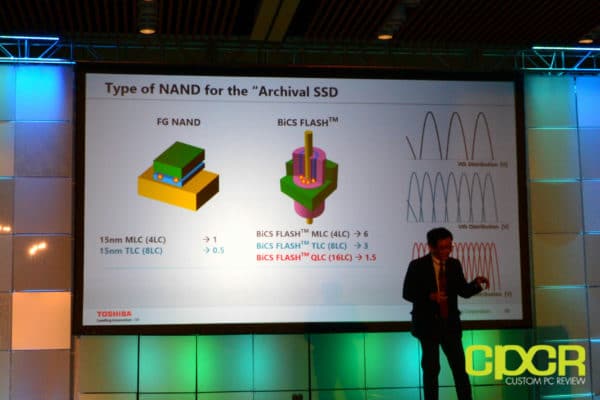

La mise au point d’une telle mémoire est très délicate, car cela suppose de pouvoir programmer dans la cellule 8 niveaux de charge, au lieu de 4 pour de la MLC ou 6 pour de la TLC. Ces niveaux deviennent très proches les uns des autres et donc difficiles à distinguer ce qui rend la cellule instable. C’est pourquoi, plus on augmente la densité d’une cellule Flash, plus sa durée de vie diminue (pour une explication plus détaillée, jetez-un oeil à notre article sur la eMLC de Micron.

Mais Toshiba assure que la structure en 3D de sa mémoire BiCS rend viable de la mémoire QLC. Selon le constructeur, de la BiCS QLC offre même une endurance plus élevée que de la mémoire MLC 2D classique (à finesse de gravure égale, en l’occurrence du 15 nm). Elle serait tout de même 2 fois inférieure à la mémoire BiCS TLC et ne conviendra donc pas aux usages les plus intensifs. Toshiba la destine en premier lieu à des SSD d’archivage, sur lesquels les données sont écrites rarement et conservées longtemps, ce qui minimise évidemment l’usure des cellules.

Toshiba n’a pas donné d’indication quant à la date de disponibilité de cette mémoire QLC.