L’Europe veut des centres de données dans l’espace

Des centres de données spatiaux afin de limiter l'impact énergétique et environnemental.

Des chercheurs établissent un record à 1,53 pétabit par seconde avec une fibre standard

La première transmission en 55 modes à un débit record de 1,53 pétabits par seconde dans une fibre optique de diamètre standard.

La GeForce RTX 4090 excelle aussi dans le cassage de mots de passe

Un RIG composé de 8 GPU pourrait venir à bout d'un mot de passe de 8 caractères NTLM en 48 minutes, maximum.

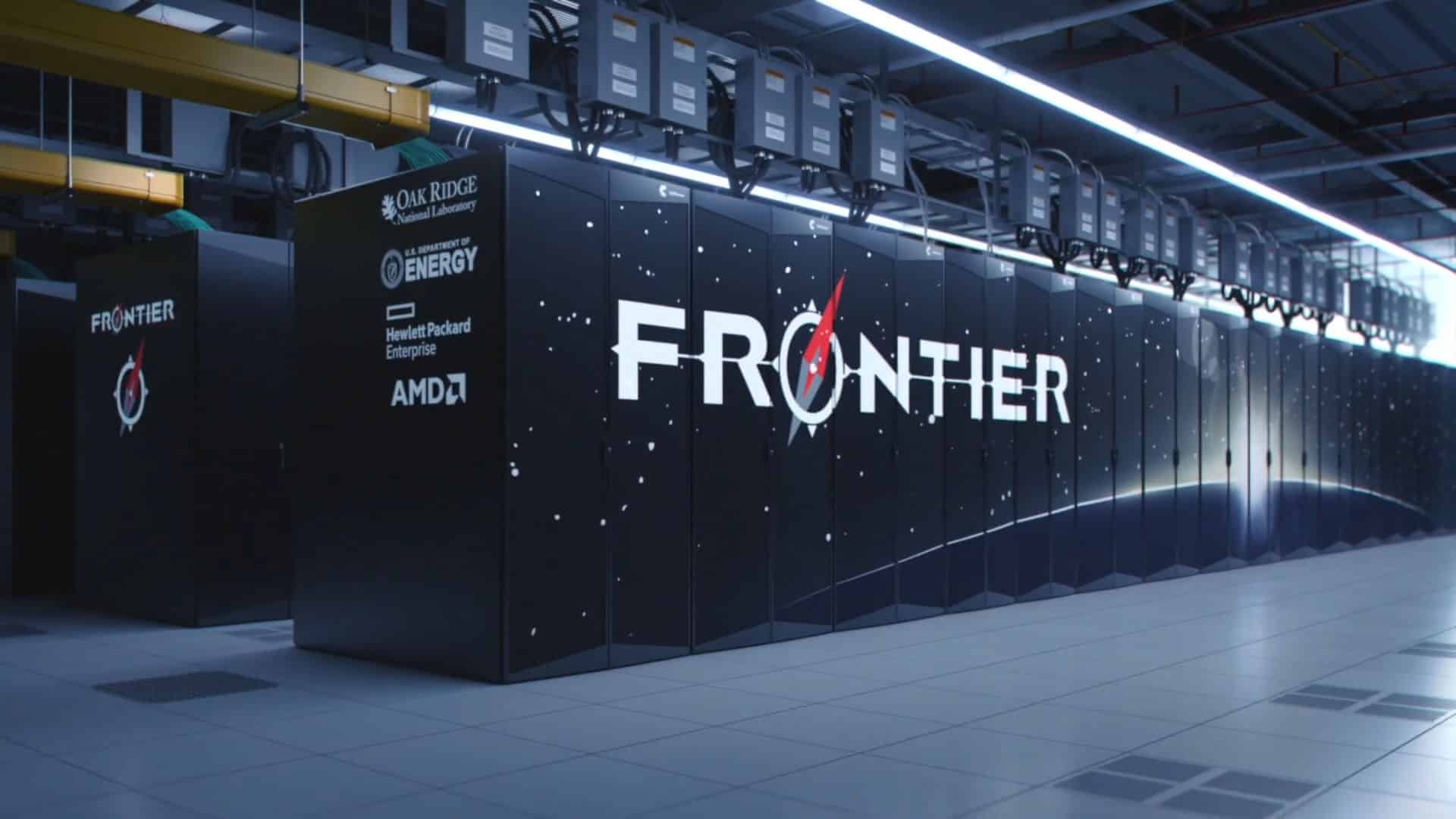

Le supercalculateur Frontier subit des défaillances quotidiennement

Bon, rien d'anormal étant donné sa complexité.

Dis Papy, comment on se connectait à Internet avant l’an 2000 ?

Ces vieux kits de connexion Internet du siècle dernier sont des trésors de nostalgie.

Le Consortium CXL présente la spécification CXL 3.0

Les CXL 1.0, 1.1 et 2.0 plafonnent à 32 GT/s ; le CXL autorise 64 GT/s.

L’ordinateur quantique de QCI résout un problème à 3854 variables de BMW en 6 minutes

Des performances 70 fois supérieures à celle du système éprouvé l'année dernière.

HAL, Ziggy, JARVIS… : ces ordinateurs qui ont façonné l’imagination

Avant-gardistes, loufoques ou spectaculairement technologiques, les ordinateurs des films, séries TV ou œuvres de fiction ont toujours forgé notre imagination. Retour sur tous les plus beaux spécimens de l'histoire de la science-fiction.

NVIDIA attaque le FSR d’AMD, les USA veulent bannir les scanners d’ASML en Chine et Bitmain lance l’Antminer E9, c’est le récap du WE

NVIDIA annonce que son DLSS est forcément meilleur que les technos concurrentes sans IA, les USA veulent interdire la livraison de scanners ASML à la Chine et Bitmain lance son nouveau mineur d'ETH.

Black Hat ou White Hat : les plus grands pirates et cybercriminels de l’histoire

Héros des temps modernes ou au contraire vils faussaires uniquement motivés par l'argent, les pirates informatiques oscillent entre deux eaux. Retour sur les plus impressionnants d'entre eux, et sur leurs principaux faits d'arme.

AMD, Apple et NVIDIA baissent leurs commandes chez TSMC, le SSD du Steam Deck plus lent, le FSR 2.0 double les FPS, c’est le récap du WE

Trois grands fabricants revoient à la baisse leurs pré-commandes chez le fondeur TSMC, Valve change en catimini les caractéristiques de son Steam Deck et un moddeur ajoute le FSR2.0 dans Cyberpunk 2077.

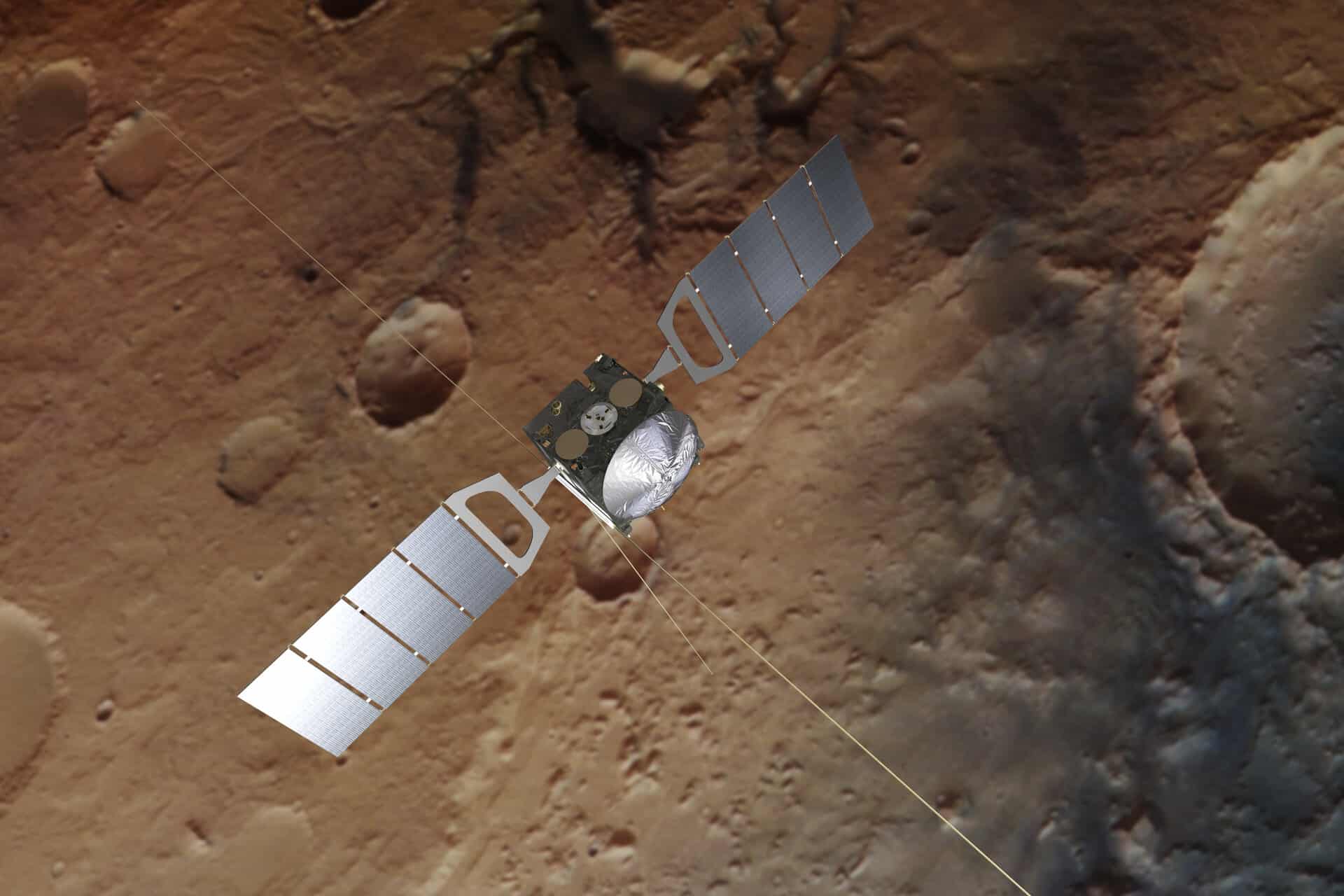

De Windows 98 à Mars 2022 : la sonde spatiale Mars Express se met à niveau

De quoi déculpabiliser ceux qui tardent à faire leurs mises à jour Windows...

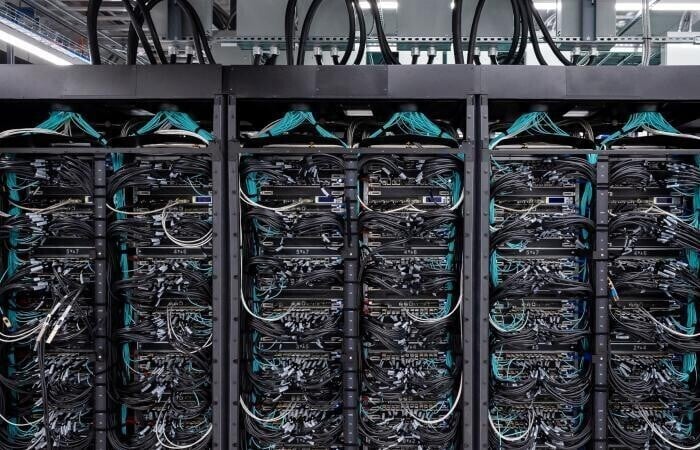

JUPITER sera le premier supercalculateur européen à atteindre l’exaflops

Un supercalculateur situé en Allemagne qui s'annonce 22 % moins gourmand que Frontier.

ISC 2022 : Intel vise le zetaFLOPS en 2027

Intel a partagé sa feuille de route pour les prochaines années. Au programme : des XPU Falcon Shores mêlant des tuiles CPU et GPU.

Frontier devient le 1er supercalculateur à franchir l’exaflop grâce à AMD

Un supercalculateur propulsé par des processeurs AMD EPYC et accélérateurs AMD Instinct.

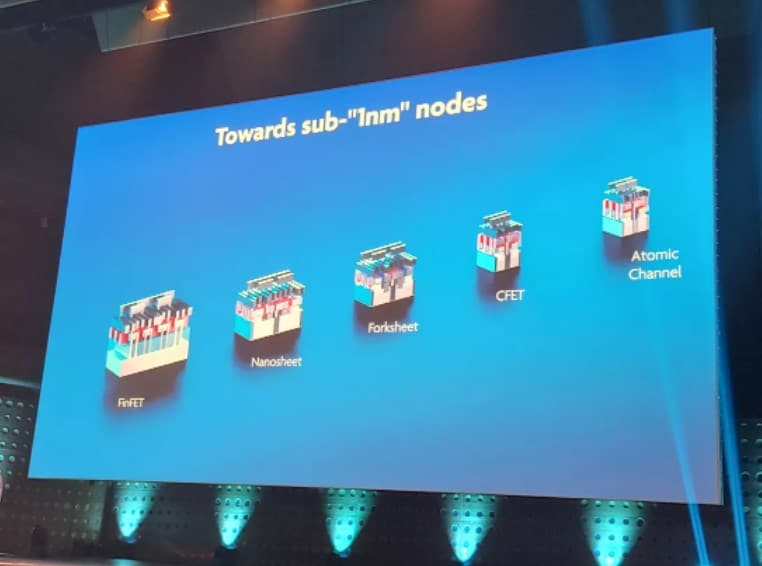

L’Imec présente sa feuille de route pour les nœuds de gravure jusqu’en 2036

Du nanomètre à l'angström ; l'institut prévoit une finesse de gravure inférieure à 1 nm vers 2030.

La startup française Greenerwave travaille sur une technologie de réflecteurs intelligents capable d’orienter les ondes électromagnétiques

Des applications prometteuses pour la 5G millimétrique.

CPL, WiFi, Ethernet : bien connecter un PC loin de sa box, un cauchemar ? Nos solutions

WiFi, Ethernet, CPL... Voici le récit d'un petit cauchemar bien réel, celui qui consiste à connecter son ordinateur de manière fiable et performante lorsqu'il est loin de la box principale du foyer.

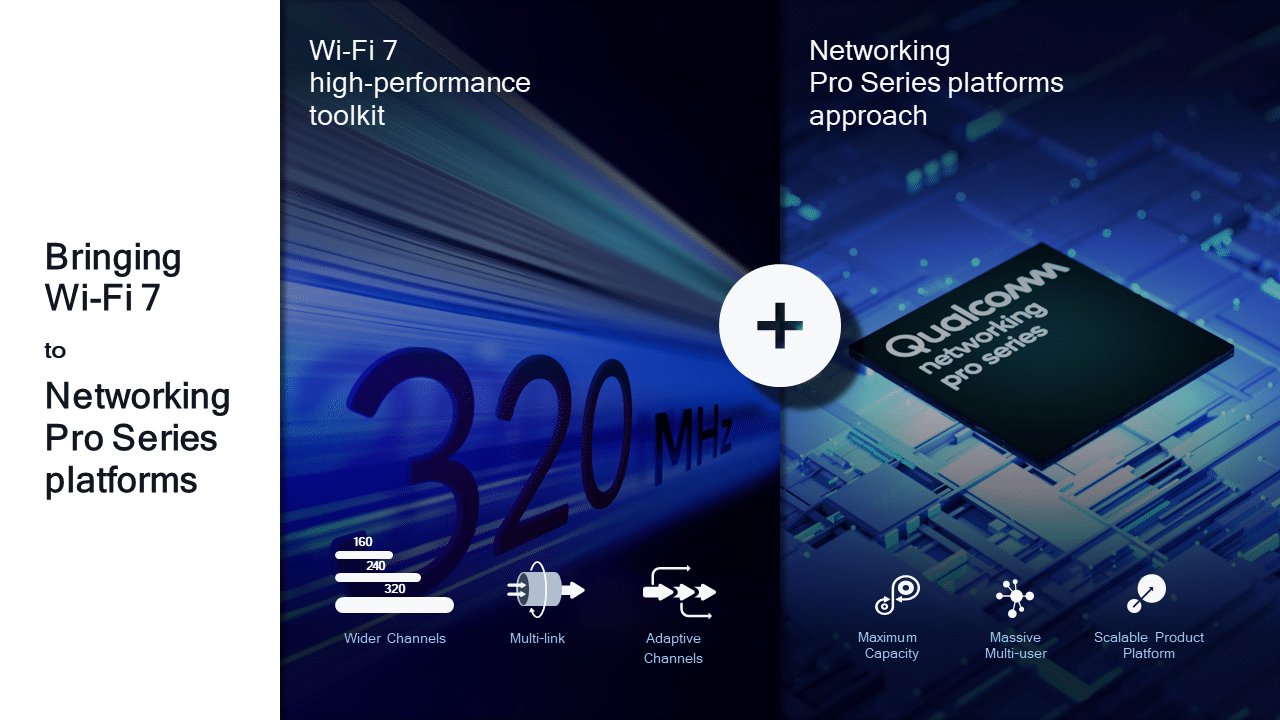

Qualcomm présente ses solutions Wi-Fi 7 : jusqu’à 33 Gbit/s

L'entreprise américaine détaille ses premiers produits Networking Pro Series Gen 3.

[MWC] Qualcomm : le modem Snapdragon X70 dope la 5G avec de l’intelligence artificielle

Qualcomm vient d'annoncer son Snapdragon X70, un modem compatible 5G (sub-6GHz et mmWave) boosté à l'IA.

[MWC] Qualcomm : les premiers appareils compatibles WiFi 7 sur le marché d’ici la fin de l’année ?

Oubliez le WiFi 6E, la version 7 de la norme sans fil est déjà à notre porte. Et c'est Qualcomm qui dégaine le premier.

Des chercheurs du MIT sont parvenus à maintenir des états quantiques pendant 10 secondes

Un record rendu possible par la découverte de nouveaux qubits.

Le Wi-Fi 6 / 6E supplantera le Wi-Fi 5 en 2022 selon TrendForce

Une norme inaugurée fin 2019 ; le Wi-Fi 7 est prévu pour fin 2023.

Il fabrique la batterie ‘portable’ avec la plus grande capacité au monde

27 000 000 mAh, et la possibilité de charger jusqu’à 60 smartphones / ordinateurs simultanément.

Le JEDEC publie les spécifications officielles de la HBM3

Jusqu'à 819 Go/s et une tension de fonctionnement abaissée à 1,1 V.