Apparue sur le marché en 2015 pour remplacer la GDDR5 sur l’autel de la bande passante, la mémoire HBM en est déjà à sa deuxième version, et la mémoire HBM3 est déjà en préparation, de même qu’une version à bas coût. De quoi la faire adopter en masse ?

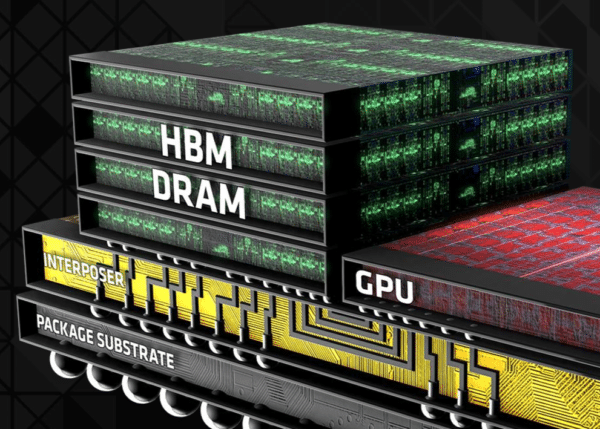

Devant les difficultés pour la mémoire GDDR5 à offrir une bande passante plus importante sans augmenter de manière trop sensible la consommation, AMD a fait le choix dès 2015 de la mémoire HBM – High-Bandwidth Memory – pour ses Radeon les plus puissantes. Avec une bande passante totale de 512 Go/s, la mémoire HBM de Hynix était alors sans concurrence. Depuis, Samsung a lancé la production de masse de sa mémoire HBM2, utilisée entre autres par NVIDIA pour sa puce Tesla P100. Hynix devrait de son côté commencer à fabriquer en masse sa propre mémoire HBM2 d’ici la fin du trimestre.

| A lire aussi : – Les Radeon Vega 10 sortiraient en mars 2017 avec de la HBM2 – AMD Radeon R9 Fury X : que valent Fiji et la mémoire HBM ? – SK Hynix est en retard sur la mémoire HBM2 – Samsung débute la production en masse de la HBM2 |

Le futur : HBM3 plus rapide, ou HBM « Low Cost »

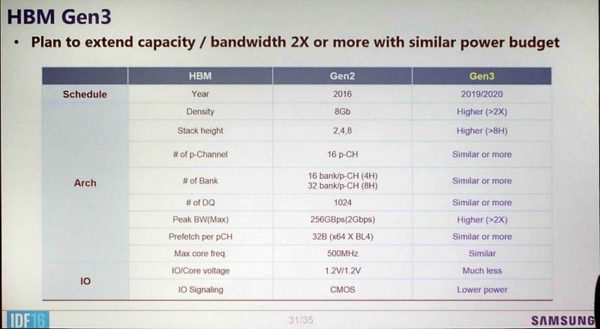

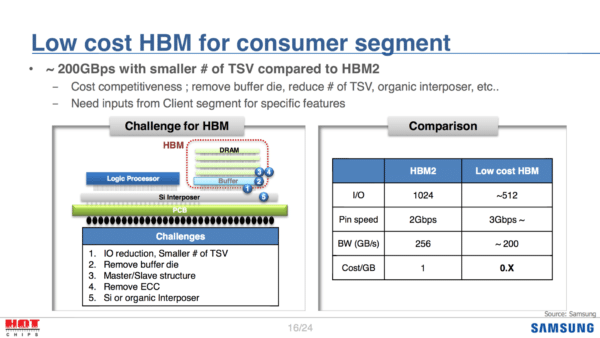

Les deux constructeurs ont présenté leur vision du futur de la mémoire HBM à l’occasion de la conférence Hot Chips 28. Deux solutions semblent se dessiner : la première avec une mémoire HBM3 (ou xHBM pour Extreme HBM, selon les termes de Samsung) encore plus rapide, la seconde avec une mémoire HBM aux coûts réduits, destinée à faire adopter en masse ce nouveau type de mémoire à la place de l’actuelle mémoire GDDR5.

Les spécifications de la mémoire HBM3 sont encore loin d’être finalisées, mais les premières rumeurs laissent supposer que la bande passante atteindrait 512 Go/s par die, contre 256 Go/s pour un die HBM2. De quoi atteindre 2 To/s avec seulement quatre dies empilés, le tout sans conséquence sur la consommation ! Du côté de la version low cost, les constructeurs devraient jouer sur le nombre d’entrées/sorties pour réduire les coûts : en passant de 1024 I/O à seulement 512, on réduit d’autant le nombre de TSV (Through Silicon Vias) et donc la complexité de l’interposer, ainsi que la taille des puces. En augmentant légèrement la bande passante par pin, il est possible de maintenir une bande passante importante, supérieure à celle offerte par la HBM1. Reste à savoir si le marché acceptera cette solution face à la GDDR5x et ses possibles évolutions…