Et promet à terme une autonomie quadruplée pour les smartphones ou encore des centres de données nettement moins énergivores.

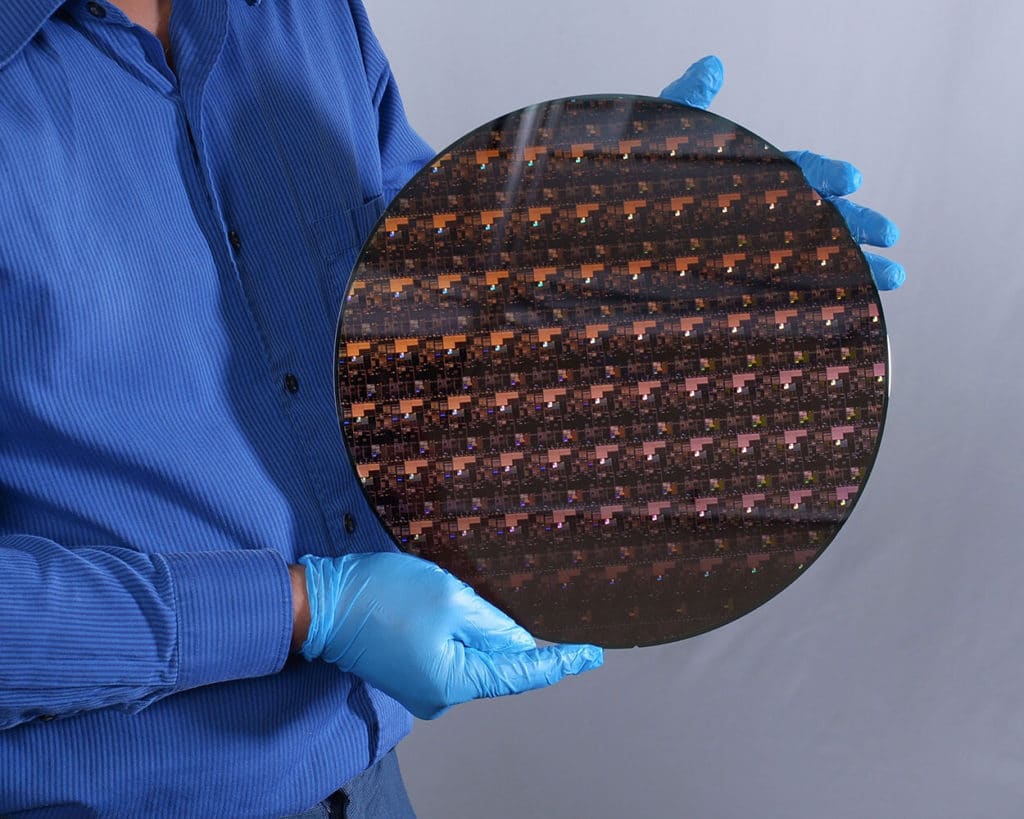

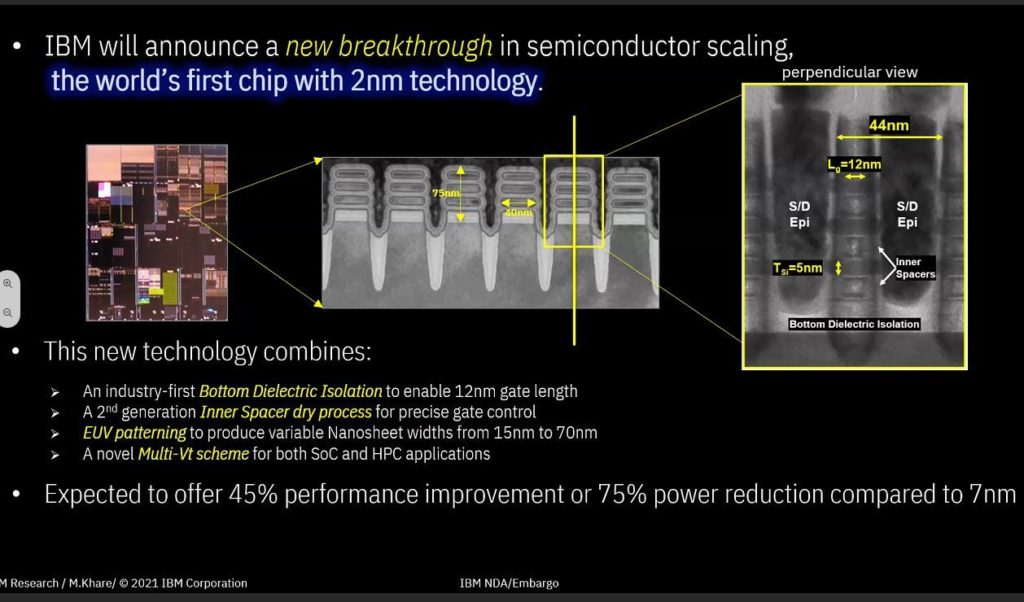

IBM a présenté une technologie de puce basée sur un nœud de gravure en 2 nm à base de nano-feuilles, une première. Selon la société, ce procédé de gravure permettra à terme de concevoir des puces avec des performances accrues de 45 % ou une consommation réduite de 75 % par rapport aux puces actuelles basées sur un nœud 7 nm. L’image qui figure ci-dessous est celle du prototype : un wafer complet de 300 mm fabriqué selon ce procédé de 2 nm au sein des labos IBM d’Albany dans l’État de New York.

En pratique, IBM argue que des puces en 2 nm seraient susceptibles de quadrupler l’autonomie des smartphones, de réduire significativement l’empreinte carbone des centres de données, de rendre les ordinateurs plus véloces ou encore d’améliorer les capacités de détection des véhicules autonomes.

Cerebras présente son Wafer Scale Engine V2 : 850 000 cœurs

Une densité de 333,33 MTr/mm2 ?

En matière de densité, l’entreprise évoque 50 milliards de transistors sur une puce de « la taille d’un ongle ». Plus précisément, il serait question d’une densité de 333,33 MTr/mm2 d’après AnandTech ; en supposant qu’elle soit authentique, cette valeur est effectivement supérieure à celle du 3 nm de TSMC.

| Finesse de gravure | IBM | TSMC | Intel | Samsung |

| 22 nm | – | – | 16,5 | – |

| 16 nm/ 14nm | – | 28,88 | 44,67 | 33,32 |

| 10 nm | – | 52,51 | 100,76 | 51,82 |

| 7 nm | – | 91,2 | 237,18* | 95,08 |

| 5 nm | – | 171,3 | – | – |

| 3 nm | – | 292,21* | – | – |

| 2 nm | 333,33 | – | – | – |

Début de production fin 2024

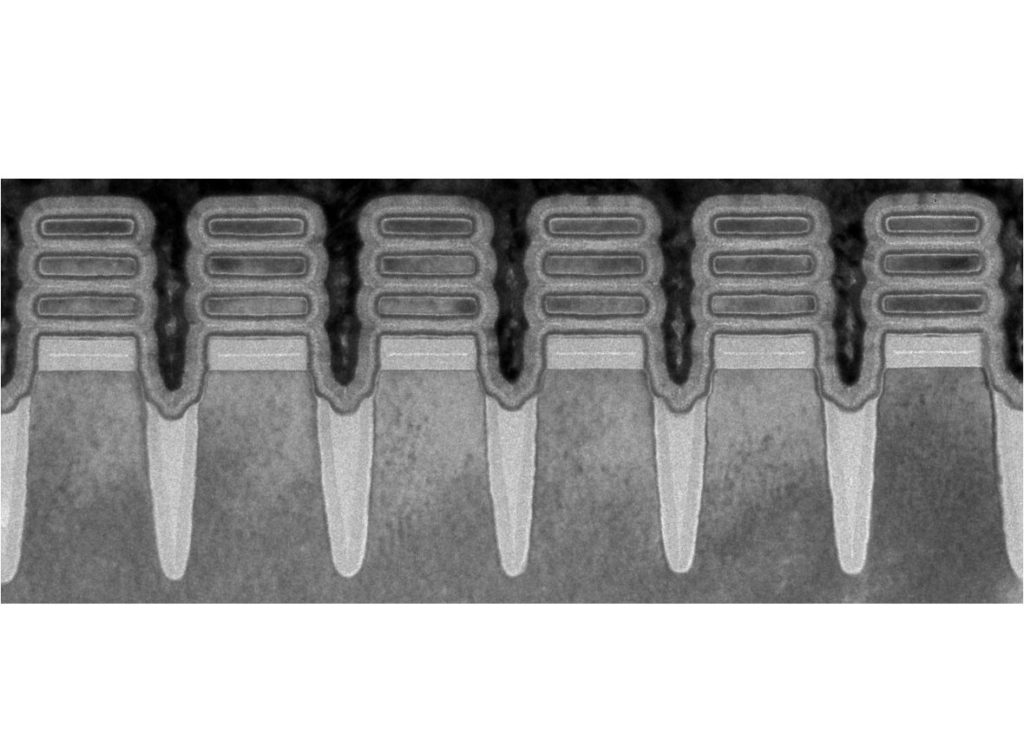

Notez qu’IBM ne produit pas de puces en masse et vend son savoir-faire et ses propriétés intellectuelles à des entreprises comme Samsung ou Intel. Comme le révèle l’image suivante d’une coupe transversale de six transistors 2 nm examinée au microscope électronique, la conception est très différente de celle d’un familier transistor FinFET.

La technologie d’IBM repose sur la technique du GAA (Gate-All-Around). Elle consiste en trois nano-feuilles de silicium empilées horizontalement, chacune étant intégralement encerclée par la grille afin de réduire les fuites (le canal de conduction d’un transistor FinFET ne l’est que sur trois faces). Chaque nanofeuille mesure 5 x 40 nm. Hauteur totale de l’ensemble : 75 nm.

Nos confrères de Tom’s Hardware US expliquent que le processus 2 nm d’IBM est le premier à recourir à la lithographie EUV sur la partie front-end-of-line (FEOL) de la puce, autrement dit celle où les transistors et les structures associées sont créés (nano-feuilles et grille). Les techniques actuelles limitent l’utilisation de la gravure EUV aux structures MOL (middle-of-line) et BEOL (back-end-of-line).

IBM fournira des détails supplémentaires dans les prochains mois. La firme prévoit que des fondeurs commenceront à graver massivement en 2 nm à partir de fin 2024.

Source : IBM