Du nanomètre à l’angström ; l’institut prévoit une finesse de gravure inférieure à 1 nm vers 2030.

La semaine dernière, l’Imec (Institut de micro-électronique et composants), a dévoilé, dans le cadre de l’évènement Future Summit à Anvers en Belgique, sa feuille de route jusqu’en 2036 pour les nœuds de processus et designs de transistors. Pour la finesse de gravure, les projections englobent donc logiquement des nœuds inférieurs à 1 nm.

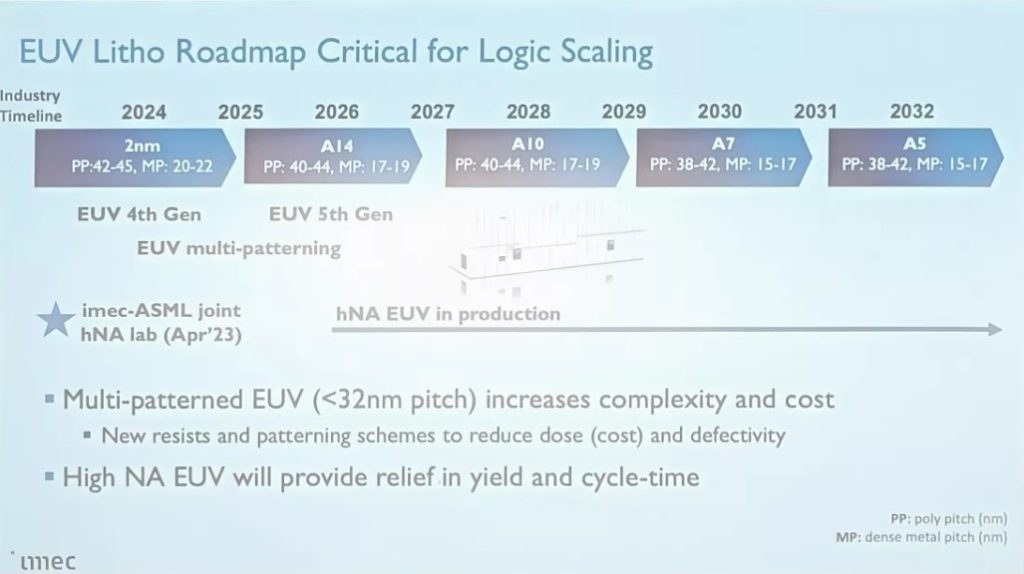

Avant toute chose, quelques mots sur l’Imec. Assez peu connu du grand public, c’est “un institut de recherche inter-universitaire flamand en micro-électronique et nanotechnologies situé à Louvain en Belgique”. L’institut collabore avec les principaux fabricants mondiaux de semi-conducteurs (TSMC, Intel, Samsung…) et autres entreprises de conception de logiciels pour semi-conducteurs (Synopsys, Cadence…). C’est également un partenaire d’ASML, la société hollandaise leader de la fabrication de machines de photolithographie (scanners EUV / DUV) ; celle-ci est d’ailleurs intervenue au cours de l’évènement.

A lire > Samsung : la production de masse en 3 nm doit débuter dès ce trimestre

L’ère du sub-1 nm en 2030

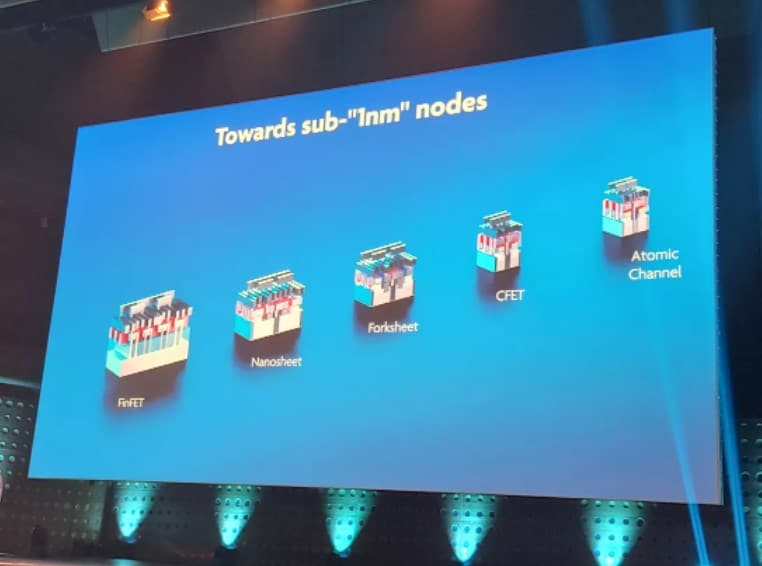

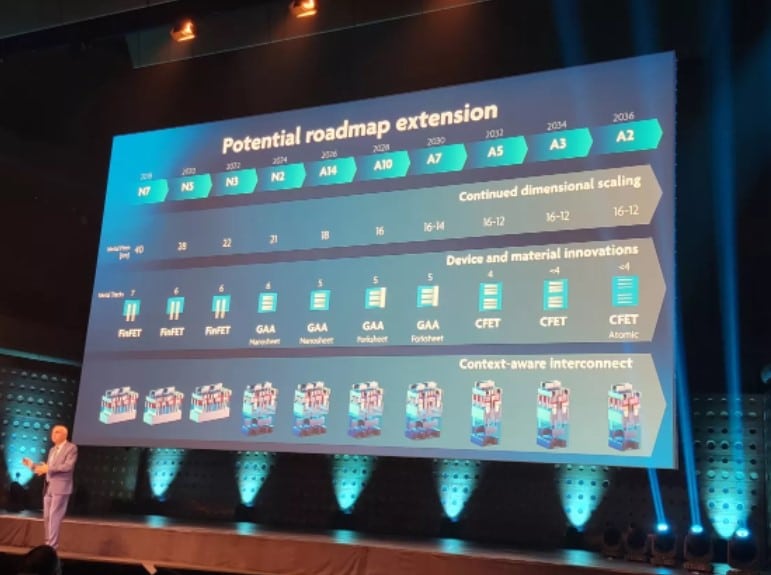

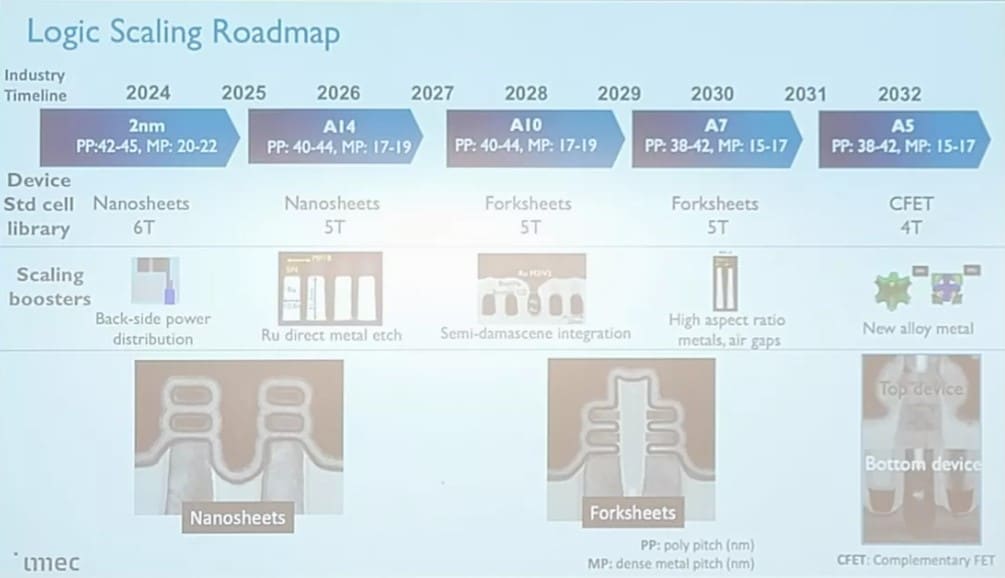

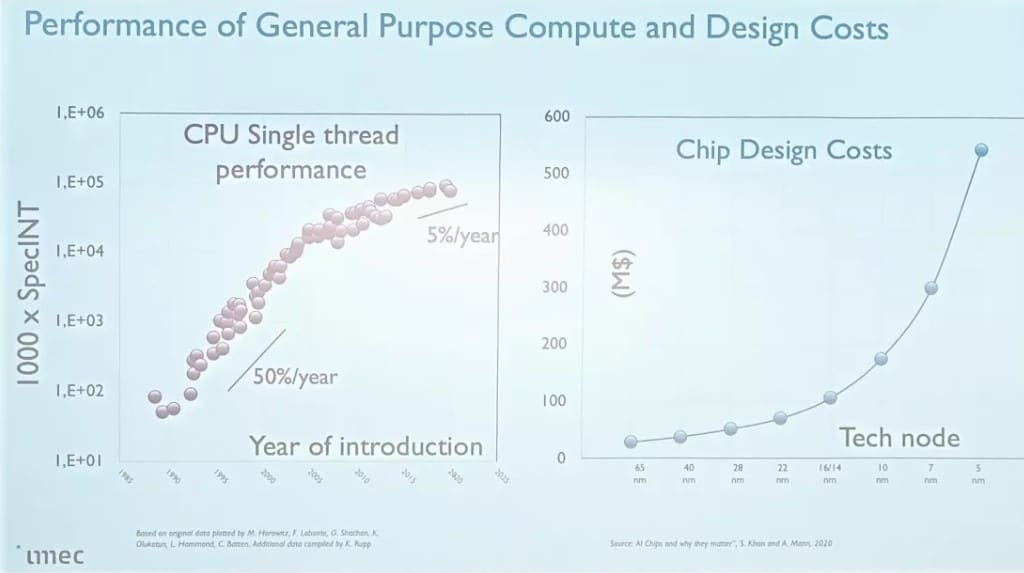

Ces précisions faites, regardons la feuille de route de l’institut. Elle mentionne des conceptions de transistors allant des désormais traditionnels FinFET (jusqu’au 3 nm), à des conceptions dites GAA (Gate All Around), du 2 nm à l’A7 (sept angströms ; un angström vaut 0,1 nanomètre). Viendront ensuite des conceptions inédites pour les nœuds A5, A3 et A2 (CFET – Complementary FET). En matière de calendrier, l’A7 ouvrira potentiellement l’ère du sub-1 nm vers 2030 ; il n’est cependant pas garanti que les concepteurs de puces suivent le même rythme, notamment en raison des coûts exponentiels.

Par ailleurs, deux diapositives présentées par ASML montraient que le DUV standard offre une densité de 100 MTr/mm2 (méga-transistor par millimètre carré) ; le 0,33 NA actuel permet une densité d’environ 500 MTr/mm2. Les machines High NA à venir (0,55 NA) la porteront à environ 1000 MTr/mm2.

A lire > C’est officiel, Intel renomme ses nœuds de gravure : l’Enhanced SuperFin 10 nm devient l’Intel 7

N’hésitez pas à consulter l’article de nos confrères de Tom’s Hardware US pour de plus amples informations. Il contient davantage de diapositifs dont certaines relatives aux défis de conception / d’alimentation qu’impliqueront les différents nœuds.

Crédit : Tom’s hardware US

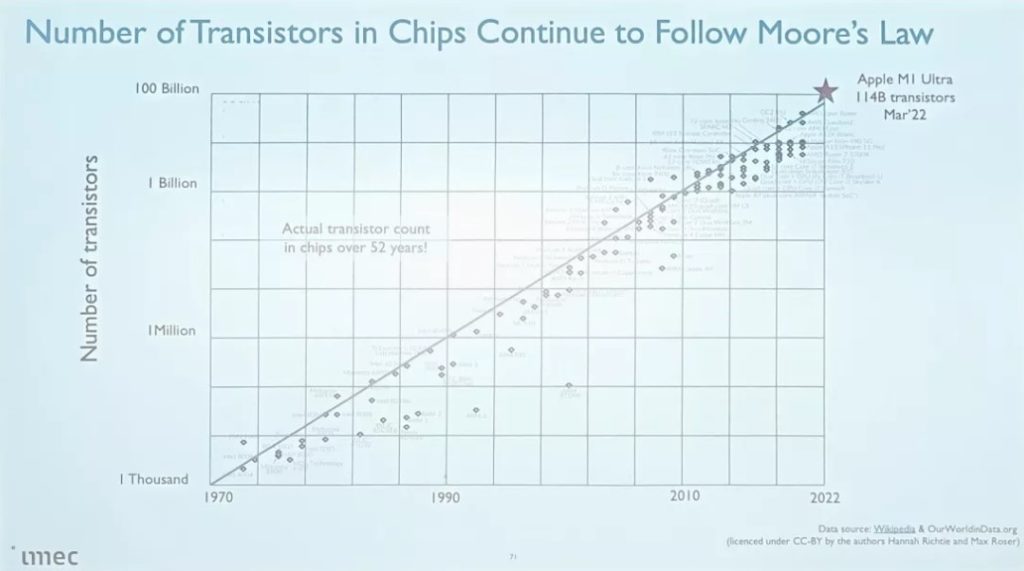

C’est fou comment la courbe de progression du CPU single thread en performance s’est littéralement tassé après les années 2010 pour finir a 5% par an ses dernières années alors qu’il était a 50% par an au début jusqu’à 2010 environ.L’ere du multi thread a vraiment pris son envol dernièrement mais jusqu’à ou, car on sait bien qu’il y a des limites au niveau logiciel.Et les coûts par machine a exploser aussi.Tous les images ici montre qu’on réduit la finesse de gravure mais on augmente sans cesse l’empilement de couche transistor de plusieurs étage, on gagne d’un côté ce qu’on perd de l’autre et qui n’est pas franchement quantifié.Mais ce que je vois aussi c’est qu’on arrive à un mur au niveau tdp qui explose littéralement tant au niveau CPU et GPU malgré des progression en finesse de gravure et en architecture, sans qu’on puisse augmenter les performances sans forcer sur les fréquences, etc, ce qui sera beaucoup plus problématique dans le futur.Les dernières séries de CPU et GPU le traduisent bien malheureusement et cela semble continuer dans l’avenir, j’espère sincèrement que cette tendance s’inversera un jour prochain.Car a un moment donné avoir trop de tdp a refroidir est impossible ou trop compliqué déjà dans une tour traditionnelle mais plus encore dans des endroits plus restreint comme dans les pc portable, all in one, mini itx, etc, je ne parle même pas des consommations folles de watt demandé qui deviennent du grand n’importe quoi aussi.Les gros défis a venir rien que pour ses partis sont très grandes.Donc va t’on avoir l’émergence et le raz de marée des processeurs arm dans les tours et pc portable, etc, d’ici 2030, peut être je serais curieux de savoir.Je ne parle des secteurs pro de recherche et de calculs haute performance ou autres secteurs qui demandent de toute façon des débauches de puissance, qui ne sont pas limité ou très peu et la recherche de performances est primordiale.