Le Stratix 10 GX 10M devance ainsi le Virtex UltraScale+ VU19P de Xilinx et ses 35 milliards de transistors.

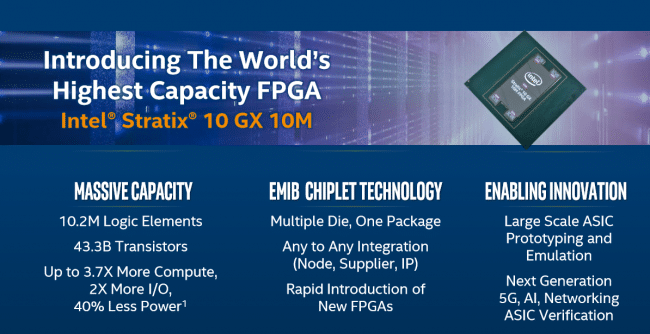

Intel présente le FPGA avec la plus grande capacité au monde : 43,3 milliards de transistors. Baptisé Stratix 10 GX 10M, il possède 10,2 millions de cellules logiques.

C’est donc mieux que le Virtex UltraScale+ VU19P présenté par Xilinx en août dernier. Celui-ci se “limite” en effet à 35 milliards de transistors et 9 millions de cellules logiques.

Plus puissant et moins gourmand

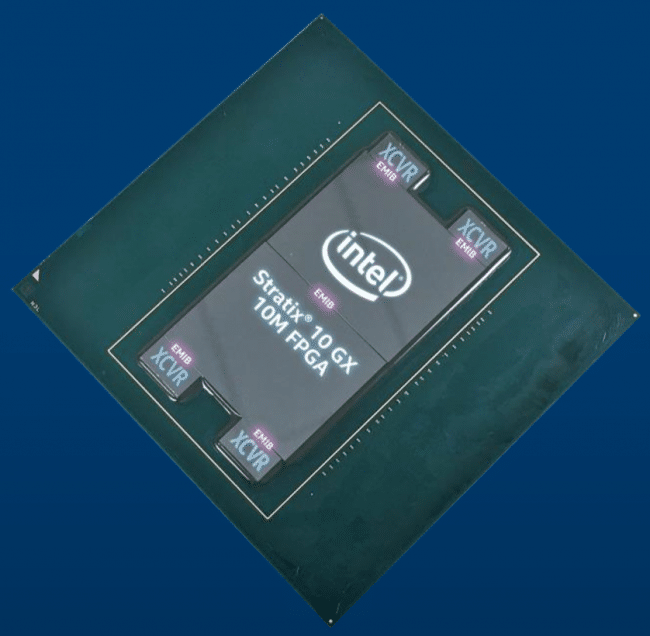

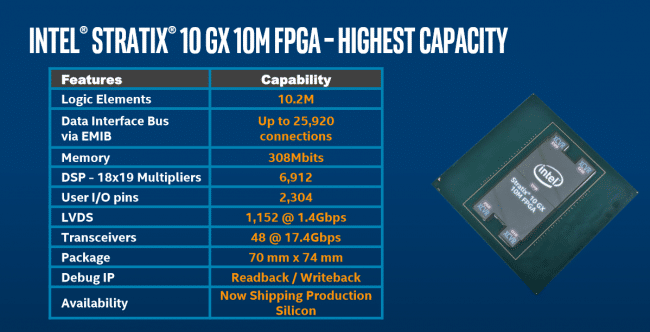

Le Stratix 10 GX 10M d’Intel combine deux dies FPGA et quatre chiplets émetteurs/récepteurs. Il a également 2304 E/S, soit un peu plus que les 2072 du FPGA Xilinx cité précédemment. Pour avoir un autre point de comparaison, on peut rapprocher ce Stratix 10 GX 10M au Stratix 10 GX 2800, l’ancien FPGA le plus puissant d’Intel. Ce dernier a 2,75 millions de cellules logiques, et 1160 E/S. L’amélioration est aussi énergétique, puisque selon Intel, à capacité équivalente, le Stratix 10 GX 10M est 40 % moins énergivore.

Pour relier les dies, Intel a recours à sa technologie EMIB 2.5D offrant 25 920 connexions. Chacune ayant un débit de 2 Gb/s, selon nos confrères de Tom’s Hardware US, la bande passante totale atteint 6,5 To/s. Toujours selon leurs estimations, ce FPGA aurait une taille d’environ 1400 mm² et une densité de 31 Mtr/mm². Enfin, notez que ce Stratix 10 est gravé en 14 nm.

Bossant dans les FPGAs je me permet de demander d’ou vient la source de Tom’s Hardware US au niveau du nombre de transistors ? L’annonce faite par Intel ne le mentionne pas.

Concernant les E/S c’est un peu plus complique que ca. Il y a plusieurs types bien distincts a prendre en compte :

– les transceivers NRZ, cad les E/S serie avec serialiseur/deserialiseur tres haut debit, typiquement max 30Gbps, utilises pour les interfaces serie type PCIe par ex, sachant qu’il faut un transceiver par ligne (un transceiver = une paire differentielle TX + une paire differentielle RX).

– les transceivers PAM4 reservés a certains modeles de FPGA dedies a ce genre d’applications, max 56Gbps

– les E/S “legacy” ou hautes tensions (cad > 1.8V, tensions malheureusement tres courantes pour connecter d’autres composants au FPGA)

– les entrees classiques ou basses tensions, le plus souvent pouvant fonctionner seules ou par paires differentielles, max 1.6Gbps

Le FPGA en question a 2304 E/S classiques, 0 E/S legacy et 48 transceivers, donc il faudra recourir a des puces externes de conversion de tension pour connecter des composants “legacy”, qui sont plutot repandus.

Le Xilinx VU19P est decline sous 2 packages, l’un avec 1664 E/S classiques, 96 legacy, 48 transceivers et l’autre avec 1976 E/S classiques, 96 legacy, 96 transceivers. Bref Xilinx a un peu moins d’E/S mais a le merite de proposer plus de souplesse avec 2 packages, et l’un propose 2 fois plus de transceivers.

Aussi au niveau fonctionnel on est d’accord que ce Stratix 10 GX 10M a pour rival le VU19P (qui a ete annonce mais n’est pas encore en production, celle-ci est prevue pour 2020, et a 35 millards de transistors), mais au niveau nombre de transistor son rival Xilinx est le Versal VC1902 et ses 37 millards de transistors qui lui est en cours de production depuis le debut de ce semestre.