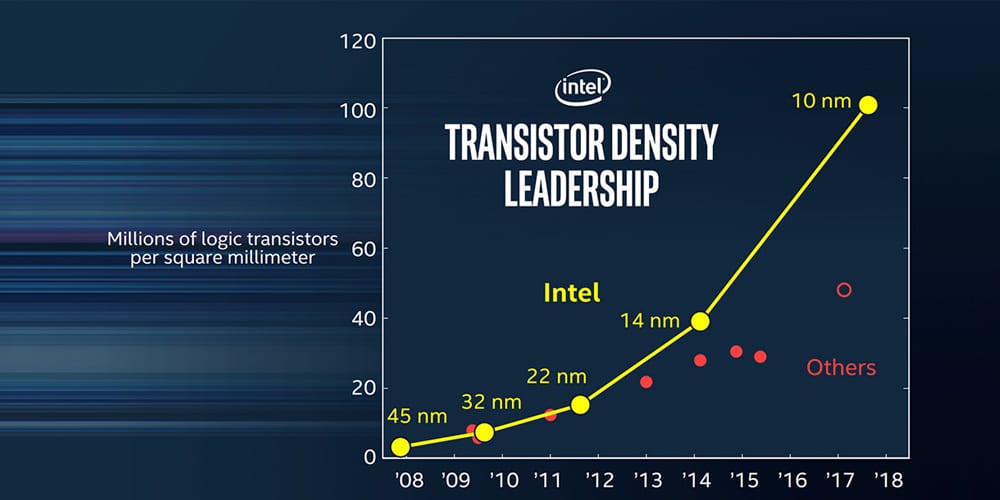

Parce que la finesse de gravure n’offre pas une densité de transistors équivalente selon les fondeurs.

Que ce soit pour les processeurs ou les cartes graphiques, la finesse de gravure est utilisée comme argument de vente par les fabricants. Si sur le marché des cartes graphiques, NVIDIA et AMD offrent maintenant des solutions basées sur des nœuds relativement proches (7 nm par TSMC pour les Radeon RX 6000, 8 nm Samsung pour les RTX 3000), pour les processeurs, il y a un véritable gouffre entre AMD et Intel : la première société propose des puces en 7 nm depuis l’été 2019, tandis que la seconde a sorti une onzième génération de Core il y a quelques jours, toujours basée sur un nœud 14 nm. Logiquement, auprès des consommateurs, cette comparaison n’est pas en faveur d’Intel.

D’après Oregon Live, Intel envisage de changer les noms donnés aux différents nœuds de gravure. L’objectif : qu’ils « correspondent à la norme industrielle » selon Ann Kelleher, directrice de de la branche développement des technologies chez Intel, qui travaille actuellement sur les nœuds 7 et 5 nm.

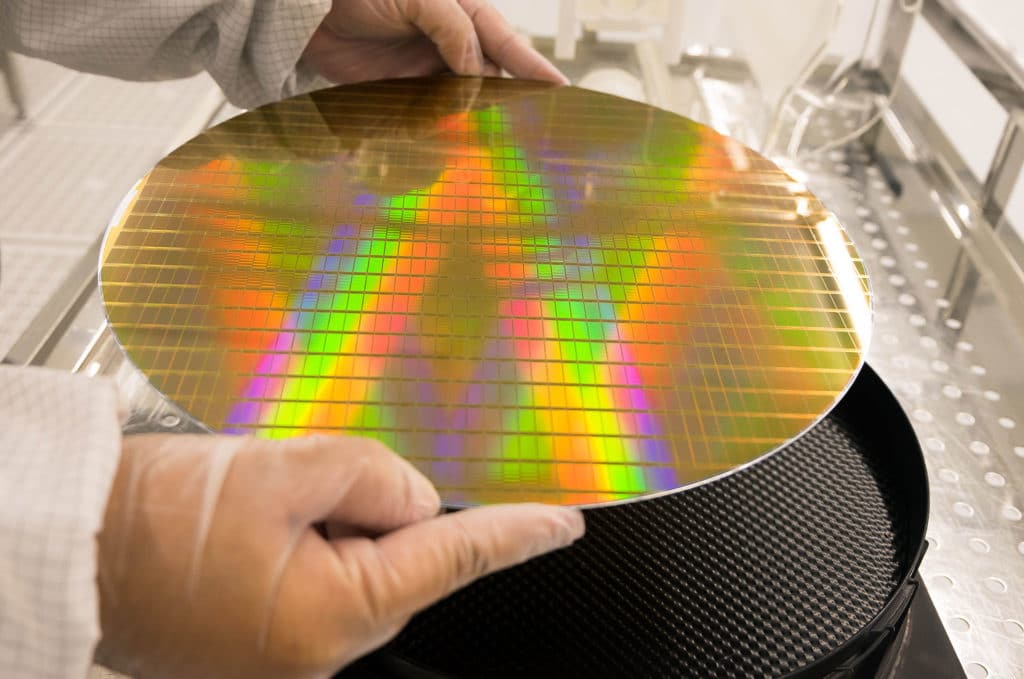

Miniaturisation des transistors et agrandissement des wafers : comprendre les enjeux technologiques

Le 10 nm d’Intel a une densité de transistors supérieur au 7 nm de TSMC

Si certains pourront voir dans ce projet une manœuvre marketing, de fait, les nœuds de gravure offrent des densités de transistors très variables selon les fondeurs. Par exemple, comme rapporté dans une précédente actu, le 7 nm de TSMC accorde une densité d’environ 90 MT/mm2 (millions de transistors par millimètre carré). Or, dans le cas du 10 nm d’Intel, la densité est de 100,8 MT/mm2. Ainsi, le nœud de gravure d’Intel en 10 nm n’est pas inférieur à celui en 7 nm de TSMC sur ce point, au contraire.

Oregon Live ne précise pas quel nouveau nom pourraient prendre les nœuds de gravure chez Intel. La voie la plus probable semble une nomenclature basée sur la densité plutôt que sur les nanomètres. D’ailleurs, ce n’est pas la première fois qu’Intel évoque l’hypothèse d’un changement de nom des nœuds de gravure. En effet, déjà en 2017, dans un article titré Let’s Clear Up the Node Naming Mess, l’entreprise plaidait en faveur d’une norme standardisée.

Comment est ce qu’on peut expliquer qu’en gravant plus fin TSMC n’arrive pas à la densité d’Intel?

La différence c’est qu’on peut les empiler, il me semble que c’est justement ce que fait Intel. Du coup ils compensent la densité avec le volume.

Ah enfin, c’était justement la question que je me posais depuis longtemps !

TSMS / Samsung mesurent peut-être leurs transistors dans la largeur et Intel en diagonale ou grande longueur ?

+ une notion de pas (espace) entre deux transistors ?

Allez, Intel, on sent enfin l’influence d’avoir un ingénieur à sa tête 😎

la finesse influençant la consommation j’espère qui continueront à communiquer dessus

Encore du intel qui essaye d’expliquer ses déboires et de compenser comme il peut.

intel nous a toujours baratiné et continue à le faire.

bjr

petite coquille

“Parce que la finesse de gravure n’offre par une densité ” “n’offre pas” plutot.

En effet merci, c’est rectifié !

Densité supérieur en théorique

Mais inférieur a 2 3 fois en réel , donc bon osef de leur chiffre