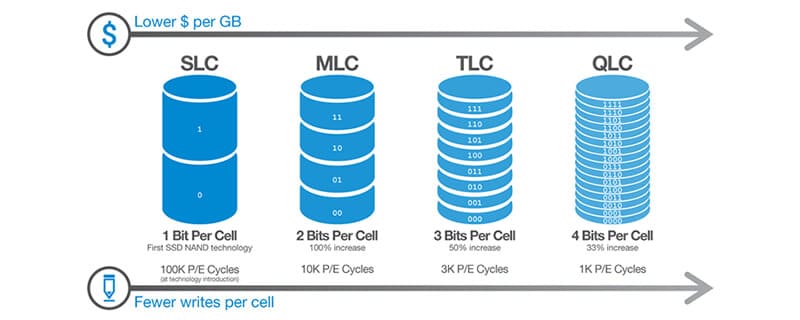

Elle couple la densité de la mémoire QLC à la vitesse de la mémoire SLC.

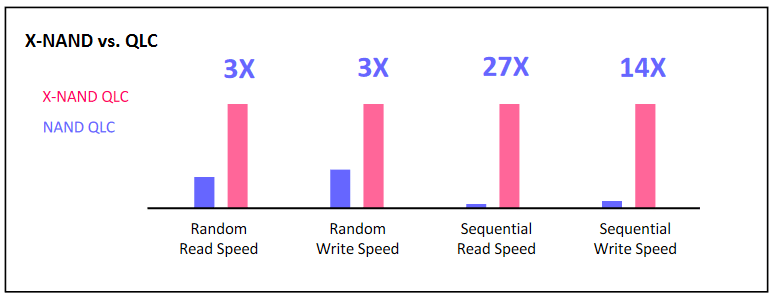

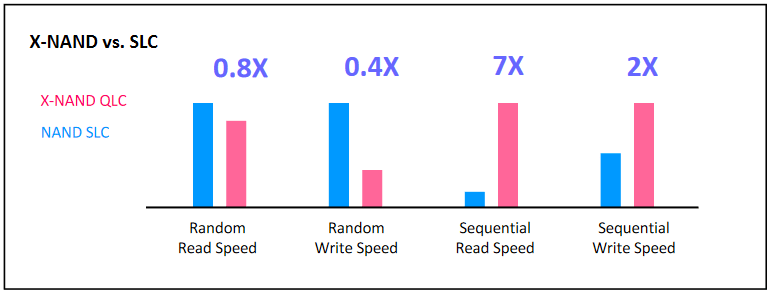

Présentée l’année dernière à l’occasion de la Flash Memory Summit 2020, la X-NAND de l’entreprise Neo Semiconductor est désormais brevetée. Dans les grandes lignes, cette mémoire ambitionne de combiner vitesse de la mémoire SLC (Single-Level Cell) et densité de la mémoire QLC (Quad-Level Cell). Selon la société, la X-NAND multiplie la vitesse de lecture/écriture aléatoires de la QLC NAND par trois et la vitesse de lecture/écriture séquentielle de 15 à 30. Neon Semiconductors propose les tableaux d’estimation des performances ci-dessous.

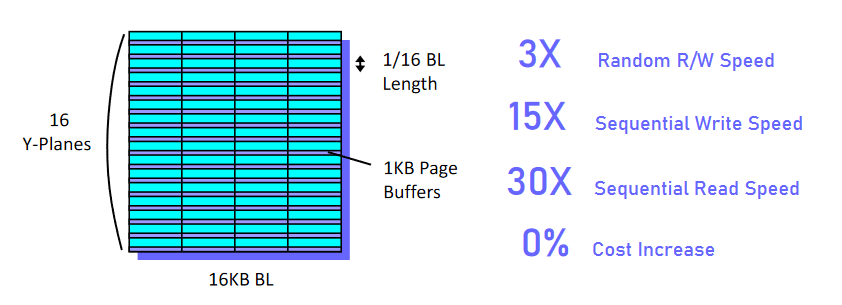

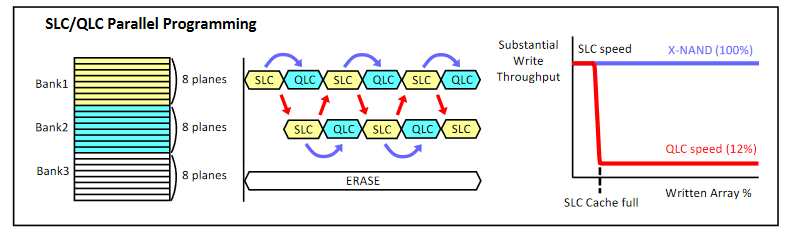

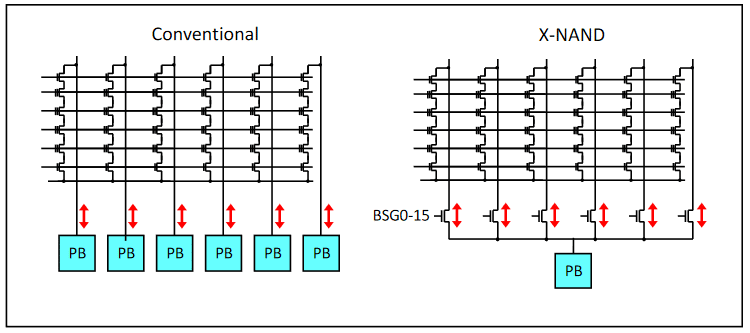

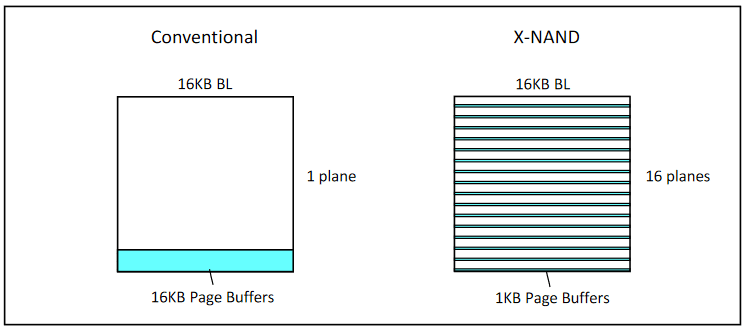

La X-NAND veut rassembler le meilleur des deux mémoires susmentionnées sans changer le format des dispositifs NAND et avec une intégration transparente au sein des systèmes. Pour y parvenir, l’architecture X-NAND est conçue de telle manière qu’elle “permet à un tampon de page d’effectuer des opérations de lecture et d’écriture sur 16 lignes de bits ou plus. Cela permet de multiplier par 16 ou plus le nombre de plans dans la direction Y sans augmenter le nombre total de tampons de page. Par conséquent, les débits de données en lecture et en écriture sont multipliés par 16. De plus, comme la longueur et la capacité de la ligne de bits sont réduites à 1/16, la vitesse de lecture aléatoire et la vitesse de vérification du programme sont considérablement augmentées. La consommation d’énergie de la ligne de bits est également réduite à 1/16”.

Kioxia teste de la mémoire 3D NAND à 6 bits par cellule

Bientôt des puces X-NAND fabriquées par un géant du secteur ?

Si vous souhaitez approfondir le sujet, vous pouvez accéder à un livre blanc de 2 pages ici ou à un autre plus étoffé de 16 pages là.

Précisons également que Neo Semiconductor est une firme californienne fondée en 2012. À ce jour, elle a plus d’une vingtaine de brevets à son actif. Elle ne fabrique pas elle-même ses puces mémoire mais vend ses licences à des clients. L’avenir nous dira si des sociétés comme Micron, SK Hynix ou Samsung décident d’intégrer cette X-NAND à leur catalogue.