Le lancement des versions pour PC fixes pourrait donc avoir lieu d’ici quelques semaines.

Depuis la mi-mai, on sait que les APU Renoir pour PC fixes d’AMD se déclinent en Ryzen 7 à 8 cœurs / 16 threads, Ryzen 5 à 6 cœurs / 12 threads et Ryzen 3 à 4 cœurs / 8 threads. On sait également qu’il y a deux séries, la G avec des puces ayant un TDP de 65W et la GE regroupant les puces avec un TDP de 35W. Au sein de ces deux séries, chaque modèle est en double, avec une version « standard » et une version pro. Parmi les autres informations à notre disposition, on suppose que les APU Renoir font l’impasse sur le PCIe 4.0, mais qu’ils proposent du PEG x16 et offrent une faible latence mémoire. Reste une grande inconnue : la date de lancement. De toute évidence, celle-ci serait proche.

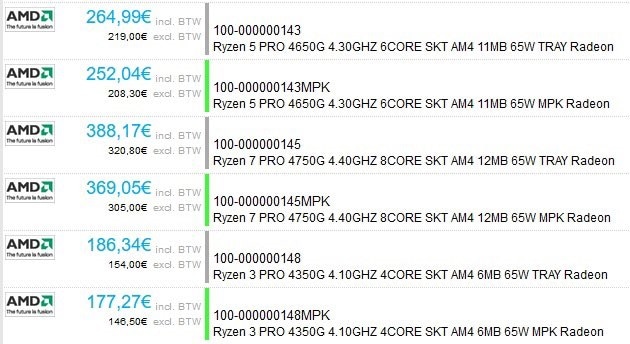

Le revendeur néerlandais Centralpoint a en effet listé trois APU Renoir sur son site. Il s’agit des Ryzen Pro 4750G, Ryzen 5 Pro 4650G et Ryzen 3 Pro 4350G. La mise en stock aurait lieu le 17 juillet prochain. On peut donc miser sur un lancement dans les semaines suivantes. En ce qui concerne les tarifs, ils sont respectivement de 305, 208 et 146 euros HT environ (versions MPK).

AMD : les Ryzen 4000 sont prêts

Fréquence maximale de 4,4 GHz pour les Ryzen 7

Rappelons que ces APU Renoir bénéficient d’une architecture CPU Zen2 et d’une architecture GPU Vega. Ils sont gravés en 7 nm. Sur le plan des spécifications, les modèles Pro ne diffèrent pas des versions classiques. Les valeurs divulguées par Centralpoint sont conformes à celles que nous connaissions. On retrouve des fréquences maximales de 4,4 GHz pour les Ryzen 7, de 4,3 GHz pour les Ryzen 5 et de 4,1 GHz pour les Ryzen 3. Enfin, la quantité de cache totale est de 12 Mo pour les premiers, (4 Mo de cache L2 et 8 Mo de cache L3), 11 Mo pour les seconds (3 Mo de cache L2 et 8 Mo de cache L3), 6 Mo pour les troisièmes (2 Mo de cache L2 et 4 Mo de cache L3).

Ryzen 3 à 4 cœurs / 12 threads

ils sont passé de 8 à 12, quel exploit ^^

Le titre est trompeur vu qu’on peut acheter des APU Renoir (Ryzen 4000) depuis mai. Vous auriez du écrire “APUs Renoir pour socket AM4” ou pour desktop ou qqch comme ca. Dans votre article on a l’impression que les versions pour portables n’existent meme pas… Sachant que l’intérêt principal de ce genre de puce est d’être utilise dans un portable…

Et encore, les 4x00H sont systematiquement dans des portables avec cartes graphiques séparées donc je ne pense pas qu’ils soient utilises en tant qu’APU. Et pourtant les medias nous ont parlé essentiellement des 4x00H puis desormais des 4x00G/GE. Pour moi le point fort de cette serie sont les 4x00U. Ce ne sont pas encore les APUs d’exception tant attendus depuis qu’AMD a rachete ATI mais ils sont bons, surtout grace a leur CPU. Dommage qu’AMD ne prevoit pas d’inclure autre chose que du Vega dans ses APUs avant au moins un an.

Je pense que tu te trompe, a mon avis ils est prevus que cpu, gpu et ram soit reunis. Je parle de gros gpu… C’est ce qui reduira au maximum les latences.