Introduction

En 1954, un transistor coûtait 5,52 $ (l’équivalent de 34,70 € aujourd’hui en tenant compte de l’inflation). En 2004, le transistor ne coûtait plus qu’un nano dollar (un milliardième de dollar américain) et en 2005, les prix baissaient tellement que c’est le coût d’un bit de DRAM (soit l’équivalent de trois transistors) qui descendait à un nano dollar.

Selon la Semiconductor Industry Association (SIA), si le marché des transports aériens avait connu la même croissance, un voyage en avion entre Paris et New York, qui coûtait 900 $ en 1978 (l’équivalent de 2 300 € aujourd’hui) et prenait 7 heures de vol, n’aurait demandé qu’une seconde et un centime de dollar en 2005.

En 1965, Gordon Moore, cofondateur d’Intel et employé de Fairchild Semiconductor à l’époque, a constaté que le nombre de composants sur un circuit intégré doublait tous les deux ans et postulait que ce rythme serait inchangé. Il a ensuite révisé son constat en 1975 pour expliquer que le nombre de transistors présents sur le die d’un microprocesseur suivait cette progression. Cette affirmation est restée plus ou moins vraie durant l’histoire des CPU, mais au-delà des considérations pseudo-scientifiques que certains lui attribuent, les énoncés de Moore furent surtout un objectif que les fabricants de processeurs ont tenté d’atteindre, entrainant avec eux le reste de l’industrie du semi-conducteur. Pour arriver à leurs fins les fondeurs jouent sur deux principaux facteurs, la taille du wafer (la galette sur laquelle sont placés les transistors) et la finesse de gravure du die (le groupe de composants qui représentera une puce).

Il est donc temps de revenir sur ces deux concepts fondamentaux pour voir ce qui se cache derrière les termes techniques que nous employons fréquemment dans nos colonnes et les défis technologiques auxquels sont confrontés les acteurs de ce marché. Ce traitement n’a aucunement la prétention d’être exhaustif et la vulgarisation de certaines des notions présentées est avant tout destinée à permettre à l’ensemble de nos lecteurs de comprendre les grandes lignes de cette industrie et abolir certaines idées reçues. De plus, par soucis de concision et éviter d’être redondant, nous ne reviendrons pas sur le processus de fabrication du processeur que nous avons déjà rapidement balayé dans notre reportage photo « La fabrication d’un processeur en images ».

Finesse de gravure : signification et pertinence

La finesse de gravure telle qu’elle est utilisée dans le commerce

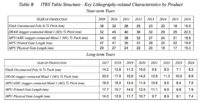

Concrètement, c’est donc elle qui va établir si un processus de fabrication se nomme 90 nm ou 65 nm. Contrairement à ce que beaucoup de personnes pensent, avant d’être une mesure, l’ITRS explique que le processus de fabrication tel qu’il est employé dans le commerce « est un indicateur des progrès généraux de l’industrie dans la miniaturisation des circuits intégrés ». De nombreux aspects du transistor présents sur la galette sont plus grands ou plus petits que cette valeur. Le processus de fabrication sert donc à ce niveau-là de label clarifiant le franchissement d’étapes importantes.

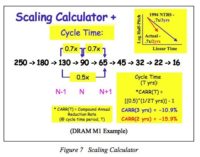

L’ITRS ne choisit pas le processus de fabrication au hasard. La valeur en nanomètre présentée au public obéit à un calcul théorique précis qui veut que chaque nouvelle finesse soit le produit de l’ancienne multipliée par la racine carrée d’un demi (0,7 environ). Le raisonnement est que chaque processus de fabrication représente un cycle technologique qui double la densité des composants sur une même surface. Cela permet aussi de laisser vivre chaque processus de fabrication suffisamment longtemps pour le rentabiliser et avoir le temps de résoudre les problèmes de la prochaine finesse. En effet, chaque étape a des ramifications énormes sur l’ensemble des composants présents sur le wafer. En espaçant ainsi les objectifs à franchir, l’ITRS limite le nombre de défis technologiques à relever d’un seul coup et facilite les transitions.

Le demi-pitch de DRAM : la référence des experts

Le demi-pitch de DRAM : la référence des experts

Si la finesse de gravure est donc avant tout un label officialisé par l’ITRS qui repose sur des calculs théoriques et qui aide les fondeurs à clarifier les étapes technologiques qu’ils franchissent, son origine repose sur une mesure physique précise. En principe, le processus de fabrication est censé représenter la moitié du petit pitch des lignes métalliques. Le pitch est égal à la « largeur minimale du métal de connexion additionnée à celle de l’espace entre les deux pistes adjacentes interconnectées » (définition extraite de la thèse de Mikael Cimino).

L’ITRS utilise le demi-pitch comme référence, car de nombreux aspects du transistor sont proportionnels à cette mesure. Par exemple, la grille du transistor représente généralement entre un tiers et la moitié de cette distance. Ainsi, un wafer d’Intel ou AMD utilisant un procédé de fabrication de 65 nm aura une grille d’une longueur de 35 nm. Bref, contrairement aux idées reçues, la finesse de gravure ne représente pas l’élément le plus petit du wafer.

La raison d’être de l’ITRS

La raison d’être de l’ITRS

La roadmap du demi-pitch que dresse l’ITRS sur les quinze prochaines années est destinée à aider les acteurs du marché. L’agence succède à la NTRS, l’organisme national américain pour la création des roadmaps de semiconducteurs, qui fut constituée en réponse à l’externalisation de la fabrication des outils de production, ce qui posait de sérieux problèmes de cohésions entre les équipementiers et les fondeurs. Tout comme la NTRS, l’ITRS a pour but d’aider tous ces acteurs à avoir une vision claire afin d’anticiper les évolutions du marché et les difficultés technologiques inhérentes à chaque processus de fabrication, mais elle bénéficie en plus de la collaboration des acteurs européens et asiatiques.

Elle est composée des associations européennes (ESIA), japonaises (JEITA), coréennes (KSIA), taïwaises (TSIA) et américaines (SIA) de l’industrie du semiconducteur. Les experts qui rédigent chaque année les documents détaillant les enjeux technologiques (que l’on appelle « chapitre ») ou qui siègent à ses comités sont très souvent les dirigeants de fonderies ou des acteurs importants de ce marché. Ainsi, le président du comité responsable de la roadmap de l’ITRS est aujourd’hui Paolo Gargini, directeur des stratégies technologiques chez Intel. On notera aussi la présence à cette table de Patrick Cogez, un des directeurs du fondeur franco-italien STMicroelectronics.

La pertinence du processus de fabrication

À première vue, on remarque très vite que les roadmaps de l’ITRS sont très différentes de celles d’Intel, AMD ou NVIDIA. Très précises et ne détaillant pas seulement les finesses commerciales, elles offrent des données clés permettant aux fondeurs et équipementiers de visualiser à quoi ressemblera un transistor à moyen (moins de six) et long (six à quinze ans) termes.

Vers la suprématie du demi-pitch de mémoire flash

La mémoire flash a apporté une modification importante. Jusqu’en 2005, le demi-pitch d’une DRAM était la référence ultime des roadmaps de l’ITRS, car il représentait le plus petit pitch réalisable par les fondeurs à un moment précis. Or, depuis 2005, les documents de l’agence prennent en compte les demi-pitchs des mémoires flash, car ils sont plus petits que ceux de DRAM.

Ainsi, la roadmap de 2005 de l’ITRS montre que 2007 est censé être l’année de production du demi-pitch de DRAM en 65 nm, mais qu’à cette date celui de la mémoire Flash est de 57 nm. De plus, contrairement aux roadmaps d’avant 2005 qui utilisaient le demi-pitch de DRAM pour donner une idée des avancées technologiques de l’industrie (GPU, CPU, DSP, etc.), c’est maintenant le demi-pitch de Flash qui est la mesure pertinente.

Par exemple, sur la roadmap de 2009 (la plus récente, l’ITRS ne dressant une roadmap que tous les deux ans), on peut voir que 2010 est l’année de production du demi-pitch de mémoire flash en 32 nm. Pour l’ITRS, l’année de production est celle où le leader grave entre 10 000 et 20 000 pièces commercialisables par mois, voire plus et qu’il est suivi d’au moins un concurrent dans les trois prochains mois. En l’espèce, 2010 est l’année où Globalfoundries (anciennement AMD) a rattrapé une partie de son retard sur Intel et commence à graver en masse ses premiers processeurs en 32 nm (cf. « Le Bulldozer d’AMD taped out »). On remarque donc une certaine corrélation entre les processus de fabrication commercialisés par les fabricants de processeurs et le demi-pitch de Flash de la roadmap de l’ITRS.

De l’imprécision apparente de la roadmap de l’ITRS

De l’imprécision apparente de la roadmap de l’ITRS

Les lecteurs les plus avertis auront constaté que la roadmap de l’ITRS planifie aussi le demi-pitch réalisable dans un microprocesseur (MPU). En 2009, l’agence affirmait que 2012 serait l’année de production du 32 nm dans les CPU, or, Intel a déjà commencé à vendre les siens et AMD n’est pas loin. Comment expliquer cette différence ? Tout d’abord, l’ITRS a tendance à être très prudente dans ses plannings, ce qui explique pourquoi les leaders de l’industrie sont presque toujours en avance sur la roadmap. De plus, comme on l’a vu plus haut, l’année de production, telle qu’elle est entendue par l’agence, est le moment où le procédé de fabrication se démocratise et non la première sortie des puces sur le marché.

Bref, il est clair que l’une des valeurs les plus importantes pour comprendre où va l’industrie est le plus petit demi-pitch de mémoire Flash. La DRAM n’est plus la référence ultime, ce qui a poussé l’agence à expliquer qu’elle gardait le demi-pitch de DRAM dans ses tableaux par souci de continuité, mais que la valeur est seulement un indicateur « historique de la miniaturisation des circuits intégrés parmi d’autres ».

Enfin, l’ITRS ne parle plus de finesse de gravure dans ses chapitres (elle a officiellement aboli le terme anglais « technological node », malgré le fait qu’il soit encore grandement utilisé par les concepteurs de puces et les fondeurs). En effet, les processus de fabrication obéissent toujours aux règles de calculs théoriques mentionnés plus haut (un nouveau procédé de fabrication est le produit de l’ancien multiplié par 0,7), mais l’agence tente d’abolir la corrélation entre les évolutions du marché et le demi-pitch de DRAM, un amalgame encore courant aujourd’hui.

Les limites des finesses définies par l’ITRS

Contraintes technologiques

En effet, avant le 350 nm, les transistors en provenance de différents fondeurs, mais utilisant le même processus de fabrication, avaient des dimensions relativement similaires. Néanmoins, il faut savoir que les fabricants sont libres de graver les transistors comme bon leur semble, les détails étant cachés derrière le voile du secret professionnel et depuis le 250 nm et le 180 nm, les fondeurs s’adaptent pour limiter les coûts. Par exemple, pour un même processus de fabrication, la longueur de la grille peut grandement varier d’un wafer à l’autre. Certains experts affirment qu’il peut y avoir des différences de l’ordre de 40 % entre deux puces censées utiliser un même processus de fabrication.

Depuis quelques années, certains fondeurs jouent la carte de la transparence et présentent souvent deux grands types de process, le premier mettant l’accent sur la fréquence de fonctionnement de la puce, tandis que le second est tourné vers la consommation. La différence réside dans les proportions des transistors. Ainsi, pour une même finesse de gravure, un fondeur qui s’oriente vers les performances utilisera par exemple des grilles plus petites et plus difficiles à produire, mais qui pourront s’ouvrir et se fermer plus rapidement, augmentant ainsi la fréquence de la puce. Par contre, une même finesse de gravure orientée vers la consommation utilisera, entre autres, des grilles plus grandes qui réduiront les problèmes de fuites de courant et ipso facto les demandes énergétiques de la puce.

Ainsi, chez Fujitsu, les puces hautes performances gravées en 180 nm avaient une grille d’une longueur de 30 nm, contre 50 nm pour celles disposant d’une consommation réduite.

Contraintes économiques

Contraintes économiques

Enfin, depuis 2001, l’ITRS avoue que le passage à de nouvelles finesses de gravure se fait plus rapidement que prévu, souvent à deux ans d’intervalle au lieu de trois auparavant (un phénomène qui a démarré durant le milieu des années 90). Elle a aussi reconnu le fait que certains fondeurs n’obéissaient plus réellement à la nomenclature en vigueur afin de commercialiser des demi-processus de fabrication (half-node) qui sont des finesses de gravure situées entre deux étapes officielles. Par exemple, entre le 65 nm et le 45 nm qui sont deux labels reconnus par l’ITRS, certains fondeurs gravent des puces en 55 nm (par exemple, les GeForce 9800 GTX produites par TSMC), le but étant de profiter de certains des avantages de l’augmentation de la finesse de gravure tout en limitant les coûts liés à la recherche et au développement.

Bref, les puces mises sur le marché sont parfois bien différentes de ce que l’on peut lire dans les chapitres de l’ITRS, certains fondeurs n’hésitant pas à se distancer des labels pour utiliser des finesses plus adaptées à leurs contraintes technologiques et économiques.

Miniaturisation et défis électriques

Ralentissements technologiques

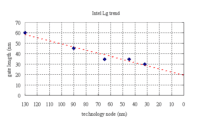

On constate néanmoins que le mouvement de miniaturisation de la longueur de la grille, tout comme celui de la longueur du canal, connaît, depuis quelques années, un ralentissement important qui est mis en évidence lorsque l’on analyse les roadmaps de l’ITRS. En 2001, l’agence affirmait que l’on graverait une grille d’une longueur de 9 nm en 2016. En 2009, elle a révisé ses estimations pour faire passer cette valeur à 15,3 nm. La réduction de l’épaisseur des couches d’oxyde de la grille a elle aussi connu une stagnation puisqu’elle n’a perdu « que » 0,1 nm depuis le 90 nm.

La raison est simple. Chaque nouvelle finesse de gravure comporte des défis physiques énormes qu’il faut parfois surmonter en faisant des compromis sur les dimensions des transistors. Ces concessions ont permis d’accélérer la vitesse à laquelle on passe d’une finesse de gravure à l’autre. En 2001, le 22 nm était prévu pour 2016. En 2009, l’ITRS le prévoyait pour 2013 (les premières puces devraient arriver plus tôt), 2016 devant accueillir, selon les prévisions les plus conservatrices, le 16 nm.

Les problèmes de fuites de courant

Les problèmes de fuites de courant

Si chaque processus de fabrication a des difficultés qui lui sont propres, on retrouve très souvent un problème commun à chaque étape de miniaturisation, celui des fuites de courant. Concrètement, ce phénomène quantique se manifeste par la présence d’un courant électrique parasite circulant à des endroits où il ne devrait pas, ce qui est très problématique lorsqu’un transistor, censé être éteint, ne peut plus contenir le courant ou que la consommation de la puce augmente trop, car il faut un courant plus élevé pour faire traverser le même nombre d’électrons d’un bout à l’autre du transistor parce qu’une partie plus importante se perd. Très grossièrement, on peut comparer cela à un tuyau d’arrosage percé. Ces problèmes augmentent la chaleur interne, limitent la fréquence atteignable et peuvent aussi nuire au bon fonctionnement des composants.

Par exemple, la réduction de l’épaisseur de la couche d’oxyde, qui joue le rôle d’isolant et qui avoisine le nanomètre (l’équivalent de cinq atomes de silicium), peut entraîner un effet de tunnel qui fait que les électrons franchissent cette barrière. Enfin, la plus grande complexité des jonctions peut aussi poser de sérieux problèmes électriques. Pour donner une ampleur des difficultés liées à la miniaturisation des semiconducteurs, on peut souligner qu’en 30 ans les fuites sont passées de moins de 10⁻¹⁰ amps/mm à plus de 10⁻⁷ amps/μm.

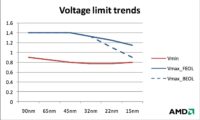

Un autre problème très courant est celui de la tension à laquelle le transistor peut fonctionner et qui se situe entre un plafond (Vmax) et un plancher (Vmin). Lorsqu’un transistor est miniaturisé, le principe veut que la tension de seuil (Vmax ou Vth) s’abaisse tandis que la tension minimale (Vmin) augmente, ce qui est problématique, car en limitant la plage de fonctionnement il est plus difficile de distinguer un état éteint d’un état allumé.

Comme l’a montré AMD dans sa dernière conférence lors du Globalfoundries Technology Conference (cf. « AMD parle 32 nm et Fusion »), les fondeurs ont réussi à maintenir les deux valeurs au fil des finesses, la tension maximale et minimale n’ayant presque pas bougé depuis le 90 nm. Néanmoins, avec le 45 nm et surtout depuis le 35 nm, Vmax amorce une descente dangereuse qui pose des problèmes architecturaux et limite le nombre de transistors que l’on peut mettre sur un die.

Les règles de Dennard

Approche à champ électrique constant

C’est à partir de cette date que les nouvelles finesses de gravure ont commencé à être réduites par 0,7, car les formules de Dennard prévoyaient que chaque nouveau procédé devait offrir une réduction de la longueur de la grille de 1/k (soit 0,7). À cette époque, la longueur de la grille était identique au demi-pitch et donc à la finesse de gravure. Il faudra attendre 1998 et le 250 nm pour voir des grilles plus petites que le demi-pitch. Le docteur a choisi 1,4 pour la valeur k par défaut, car une réduction 1/k permet de doubler la densité des transistors sur un die d’une surface identique.

Obstacles physiques et réponses pratiques à la première approche de Dennard

Obstacles physiques et réponses pratiques à la première approche de Dennard

L’approche de Dennard avait le grand avantage d’offrir une augmentation importante de la fréquence de fonctionnement. Le problème est que cette méthode repose sur l’idée que les réductions de tous les aspects du transistor sont possibles à facteur constant, ce que nous savons aujourd’hui être physiquement impossible.

Le scientifique partait, par exemple, de l’hypothèse qu’il n’y avait pas de limite au dopage (impureté volontairement introduite pour modifier certaines propriétés électriques du matériau). Ce procédé était nécessaire pour limiter la tension de seuil, mais c’était sans compter sur le fait qu’à partir d’une certaine quantité d’impuretés, les performances se dégradent et les fuites de jonctions p-n (source et drain) augmentent. De plus, même si la diminution constante de la tension était possible, d’autres aspects du transistor ne pourraient pas suivre un redimensionnement similaire. Cela entraîne inévitablement des dégradations que l’on appelle « effets de canal court ».

À partir du 130 nm, les scientifiques ont été obligés d’adapter l’approche de Dennard et sont venus avec l’échelle à tension constante (constant voltage scaling ou V=cte). Au lieu de maintenir le champ électrique, on maintient la tension en ne redimensionnant que certains aspects du transistor. Néanmoins, cette méthode a le grand désavantage de provoquer une augmentation importante du champ électrique. En 1984, Robert Dennard, avec l’aide de Matt Worderman et Giorgio Baccarani, a donc pris le meilleur des deux mondes pour proposer une méthode mixte, dite aussi généralisée, utilisant le facteur k dans certains cas et un facteur k’ dans d’autres.

Solutions architecturales aux défis électriques

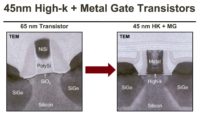

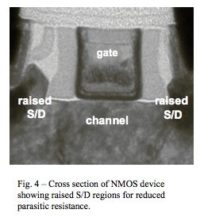

Les apports architecturaux du 90 nm et du 45 mn

L’exemple le plus commun est la stagnation de l’épaisseur de la couche d’oxyde depuis le 90 nm, ce qui a eu pour conséquence de geler les réductions de tensions et la miniaturisation de la longueur du canal. La densité thermique augmente donc plus rapidement que les performances de nos solutions de refroidissement à air et les scientifiques estimaient, il n’y a pas si longtemps, qu’un processeur monocore ne pouvait pas dépasser les 4 GHz (Ghavam Shahidi, Evolution of CMOS Technology at 32 nm and Beyond, IEEE 2007) et si certaines architectures tolèrent des fréquences supérieures (cf. « Le CPU le plus rapide du monde »), elles restent exceptionnelles. C’est la raison pour laquelle les fabricants de processeurs ont décidé de multiplier les cores, au lieu de compter sur la fréquence de fonctionnement pour améliorer les performances.

Les fabricants utilisent aussi des transistors leurres (dummmy transistors) ou des lignes métalliques leurres, qui ne sont là que pour optimiser la fabrication de la puce, et le placement des transistors fonctionnels. Des oxydes de grille leurres (dummy gate oxide) sont aussi ajoutés afin d’éviter la formation de nitrure lors de la fabrication de la couche d’oxyde de la grille. Si ces méthodes sont très anciennes, les Penryn d’Intel se sont fait remarquer par l’utilisation massive de ces procédés.

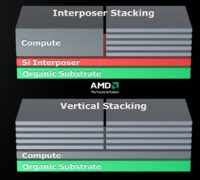

Architectures 3D ou le die stacking

Architectures 3D ou le die stacking

Le die stacking est une technologie qui fait l’objet de beaucoup d’attention, car elle permet de mettre plus de transistors dans un même package sans pour autant accroître la surface de la puce et en offrant des interconnexions plus courtes et plus performantes. Le terme die stacking regroupe de nombreuses technologies, parfois très anciennes et déjà utilisées dans les mémoires, qui ont toutes la même finalité, mais font appelle à des méthodes différentes.

L’empilement de dies différents les uns des autres ou d’une complexité importante étant beaucoup plus difficile à réaliser que l’ajout de modules Flash ou SRAM les uns sur les autres, cette technologie est pour l’instant limitée à des composants précis. Néanmoins, les fondeurs voient dans le die stacking une solution aux problèmes de consommation, car l’architecture permet d’optimiser la gestion du signal et des interconnexions plus petites produisent moins de capacités parasites. Les recherches se concentrent principalement sur le vertical stacking qui empile les dies verticalement avec des interconnexions les traversant (Through Silicon Via ou TSV) ou les contournant. Il est commun de placer une simple couche de silicium entre les dies afin d’éviter l’écrasement des fils et favoriser les dégagements thermiques.

Avant de commercialiser des puces utilisant cette technologie, qui est encore limitée à des architectures simples, les fondeurs devraient empiler les dies en utilisant la technique du Interposer Stacking. Pour faire simple, une couche de silicium est placée en bas de la pile. D’un côté, on a un processeur et de l’autre, une série de dies variés (contrôleur mémoire, mémoire, etc.) empilés les uns sur les autres. Dans cette configuration, les interconnexions partent du CPU pour traverser la couche interposée et relier la pile de dies. AMD a annoncé qu’il utiliserait d’abord cette technologie avant de passer au vertical stacking.

Dans tous les cas, le package doit pouvoir contenir l’architecture, mais aussi favoriser la dissipation thermique et protéger le tout contre les risques d’écrasement lors de l’installation d’un système de refroidissement.

Miniaturisation et défis lithographiques

La miniaturisation des procédés de fabrication passe aussi par l’amélioration de la précision des méthodes photolithographiques employées. Avec le passage au 180 nm, les fondeurs ont introduit un laser à fluorure d’argon d’une longueur d’onde de 193 nm. Pour simplifier, le laser traverse une optique afin d’imprimer un motif sur une couche photosensible, ce qui va « graver » à la finesse désirée. Avant cela, les fondeurs utilisaient un laser à fluorure de krypton d’une longueur d’onde de 248 nm.

Comprendre l’importance de la longueur d’onde

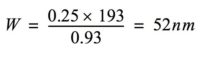

Les lois optiques nous apprennent que la finesse de gravure (W) est dépendante de la longueur d’onde du laser (λ) et l’ouverture numérique de l’optique qu’il va traverser (NA), selon la formule :

k₁ est un facteur complexe qui dépend de plusieurs variables comme la qualité de la couche photorésistante du wafer et les techniques d’amélioration de la résolution ainsi que la cuisson. Pour des raisons pragmatiques, les scientifiques estiment qu’en lithographie simple, la plus petite valeur pour k₁ est environ de 0,25 et les équipementiers utilisent souvent 0,30 comme référence.

Du temps de la photolithographie classique dite aussi sèche, la meilleure ouverture numérique possible était 0,93. En appliquant la formule, on peut voir que la plus grande finesse possible (plus le chiffre est petit, plus la finesse est grande, car plus on grave fin) avec un laser d’une longueur d’onde de 193 nm est de 52 nm.

Mathématiquement, l’ouverture numérique est égale à l’indice de réfraction du milieu d’observation (n) multiplié par le sinus du demi-angle de cône de lumière pouvant entrer et sortir de la lentille (ø)

Lithographie par immersion

Lithographie par immersion

En lithographie sèche, le milieu d’observation est l’air qui a un indice de réfraction de 1. Ainsi, l’ouverture numérique précédemment utilisée de 0,93 est en fait égal à 1 x sin(69). Néanmoins, en plongeant le wafer dans de l’eau très pure, on change l’environnement et ipso facto l’indice de réfraction qui passe alors à 1,44. En changeant ce paramètre, les équipementiers ont pu fabriquer des scanners disposant d’une ouverture numérique de 1,30 (1.44 x 0.90) et la plus grande finesse de gravure possible est donc devenue le 44,5 nm, autrement dit, le 45 nm.

On comprend donc pourquoi la très grande majorité des fondeurs ont adopté la lithographie par immersion à partir du 45 nm. Intel a néanmoins délaissé ce procédé pour continuer à utiliser une photolithographie sèche, la firme de Santa Clara n’ayant fait appel à l’immersion qu’à partir de son 32 nm. Elle a fait ce choix technologique afin d’éviter d’avoir à gérer les rendements difficiles de ce procédé lithographique encore jeune à l’époque où elle a démarré la fabrication en masse de ses processeurs en 45 nm.

Avant de nous lancer dans une description du double motif, nous tenons à préciser que de plus en plus de fondeurs combinent diverses méthodes lithographiques, les couches les plus critiques utilisant des procédés plus développés, mais aussi plus couteux, tandis que les couches moins complexes utilisent des méthodes plus anciennes et moins chères. Par exemple, Intel n’a pas hésité à revenir à une lithographie sèche avec un laser d’une longueur d’onde de 248 nm pour graver certains aspects des prototypes en 32 nm. Il ne faut donc pas automatiquement penser qu’un die utilise toujours une seule méthode lithographique.

Le double motif, un passage obligé

Deux expositions en valent mieux qu’une

Très schématiquement, on peut comparer cela à un individu qui achète et installe une palissade préfabriquée, mais qui juge que l’espace entre les pieux est trop grand. Une des solutions à ce problème est d’acheter un autre modèle identique et ficher les planches de manière à les intercaler par rapport aux premières afin de réduire l’espace disponible.

Ainsi, avec le double motif, il est théoriquement possible de réduire la taille du demi-pitch par deux, ce qui explique qu’avec des outils pouvant graver en 36 nm, on parle aujourd’hui d’aller jusqu’au 18 nm. De plus, ce procédé se prête bien à la lithographie de puces électroniques, car les motifs gravés se répètent souvent avec des distances similaires. Bref, la symétrie inhérente à l’architecture des puces signifie qu’il est facile de scinder le procédé d’exposition en deux étapes distinctes.

La trinité du double patterning

La trinité du double patterning

Le monde du double patterning regroupe une multitude de technologies qui ont toutes pour but d’exposer le wafer de multiples fois, mais qui utilisent des méthodes parfois très différentes pour y arriver. Par souci de concision et au vu de la nature de cet article, il serait inopportun de détailler toutes les méthodes développées par les fondeurs. Nous nous arrêterons donc seulement sur les trois méthodes les plus populaires.

Le litho-etch-litho-etch (LELE ou exposition-excavation-exposition-excavation) est très proche de l’analogie de la palissade. On expose le wafer, puis on retire chimiquement les parties exposées et on recommence. Pratique, cette technique a le désavantage de doubler les coûts et les temps de fabrication et de ne pas pardonner le mauvais alignement du masque. Le litho-freeze-litho-etch (LFLE ou exposition-gèle-exposition-excavation) est similaire à la première méthode, mais au lieu de retirer la première partie du wafer exposée, on gèle la galette pour ensuite procéder à la seconde exposition. Le gèle chimique appliqué évite que la première couche exposée n’interfère lors de la seconde exposition. Les scientifiques ont encore besoin de perfectionner l’étape du gel, mais le LFLE est très prometteur, car il permet une réduction des coûts par rapport au LELE.

Enfin, la technique du sidewall-spacer (espaceur de murs latéraux) gère mieux les problèmes d’alignement du masque. Elle demande la création de lignes séparées par un espace deux fois plus grand que nécessaire et qui représente les contours externes du motif. On procède ensuite à la gravure de lignes adjacentes des deux côtés des lignes modèles qui sont retirées. On se retrouve alors avec deux fois plus de lignes qu’au départ et un espace deux fois plus petit.

Le LELE et LFLE pour les processeurs et le Sidewall-spacer pour les mémoires

Le LELE et LFLE pour les processeurs et le Sidewall-spacer pour les mémoires

ASML, Canon et Nikon, les trois plus grands équipementiers, privilégient aujourd’hui le LELE et le LFLE pour des raisons techniques et commerciales, les améliorations dans l’alignement des wafers obligeant l’achat de nouvelles machines contrairement au sidewall-spacer qui peut être optimisé avec les machines existantes. Applied Materials, un autre fournisseur de scanners, se concentre quant à lui sur le sidewall-spacer. Aujourd’hui, les fabricants de processeurs privilégient souvent le LELE et LFLE tandis que les fabricants de mémoires font souvent appel au sidewall-spacer qui est plus adapté à la création de cellules de stockage. En effet, cette méthode multiplie rapidement le nombre d’expositions nécessaires lorsque la complexité de la puce approche celles des processeurs, augmentant les coûts de production.

Le double patterning en 32 nm fut démontré pour la première fois par des chercheurs belges de l’institut de micro-électroniques et composants (IMEC) en juillet 2007 et comme on a pu le voir, cette méthode lithographique permet de continuer à atteindre les objectifs de Moore. Le problème est qu’elle coûte cher et est extrêmement sensible aux erreurs, un mauvais alignement pouvant complètement ruiner toute une série de puces. Elle apporte donc une solution pour le 32 nm et le 22 nm, mais il faudra trouver de nouvelles réponses pour graver en 16 nm.

Miniaturisation et défis technologiques à venir

Craintes économiques

Les plus pessimistes estiment d’ailleurs que l’augmentation fulgurante des coûts, inhérente à chaque nouvelle étape technologique, sera le principal frein aux conjectures de Moore. C’est un argument valable qui se défend, mais il ne faut pas non plus oublier que les bénéfices liés à la miniaturisation des transistors sont une motivation énorme pour toute l’industrie qui continue de profiter d’un soutient massif des sociétés et universitaires. De plus, avec l’apparition de marchés émergents et des secteurs fertiles, comme celui des smartphones, tablettes et autres produits mobiles, les apports techniques et commerciaux qui surviennent avec chaque nouveau procédé continuent de faire pencher la balance en faveur de l’innovation.

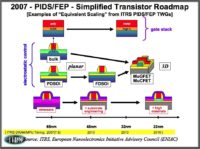

Évolution des transistors

Évolution des transistors

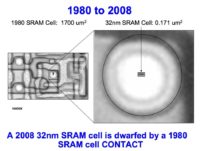

Intel commercialise déjà ses premiers processeurs en 32 nm, AMD devrait le suivre très bientôt et les premières puces avoisinant le 22 nm commencent à sortir des usines (cf. « De la flash en 2x nm chez Hynix »). Cette dernière finesse de gravure pourrait marquer un retour en arrière avec des longueurs de grilles équivalentes à la taille du demi-pitch et si les obstacles technologiques sont bien présents, les fondeurs restent confiants, car les réponses semblent être déjà trouvées.

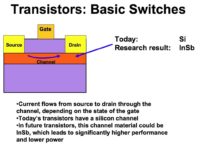

Ce procédé de fabrication devrait marquer la présence d’un nouveau matériau low-k séparant le transistor de la première couche métallique. Il verra aussi l’apparition de MuGFET (Multiple Gate FET) et MuCFET (Multiple Channel FET) qui sont en fait des transistors en trois dimensions disposant de plusieurs canaux ou plusieurs grilles et qui sont censés répondre aux problèmes de miniaturisation des modèles classiques. Dans le cas des MuGFET, les grilles peuvent être indépendantes ou contrôlées par une même électrode. Intel utilise principalement une structure avec une grille et trois canaux. Ces transistors fonctionnement de la même manière que les anciens modèles, mais répartissent les électrons sur trois canaux, ce qui permet de réduire les fuites.

Le 22 nm devrait aussi apporter une nouvelle génération de couches d’oxyde high-k utilisant du dioxyde de hafnium (comme on le fait depuis le 45 nm) dopé avec du dioxyde de silicium ou de l’oxyde d’yttrium. Les méthodes de fabrication de la grille devraient aussi changer afin d’optimiser la permittivité. Intel a déjà annoncé qu’il commercialisera ses premiers processeurs en 22 nm durant le second semestre 2011 et il est fort probable qu’il fasse appel à toutes ces innovations.

Les pistes de recherche

Les pistes de recherche

Les yeux sont donc tournés vers la prochaine grande étape technologique à franchir, le 16 nm, qui est vu par beaucoup comme un seuil physique qu’il sera difficile de dépasser. En effet, à cette taille, certains métaux de faible permittivité utilisés aujourd’hui seraient trop fragiles pour les électrons qui pourraient causer des dommages plasmiques importants lors de leur circulation. Les problèmes de fuite à cette finesse sont aussi très difficiles à gérer en raison de nombreux effets de tunnel, en plus du fait qu’il faille réduire l’épaisseur des couches d’oxyde de la grille à 0,5 nm (soit environ deux atomes de silicium).

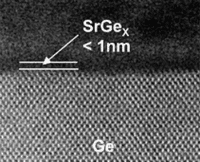

Toshiba a aussi présenté, en juin dernier, des avancés technologiques importantes relatives à la structure de nanofils permettant de miniaturiser les transistors et passer au 16 nm. Il a aussi montré en 2009 une nouvelle couche isolante composée d’un film de strontium germanium (SrGex) de 0,1 à 0,2 nm d’épaisseur pris en sandwich entre du germanium et de l’aluminate de lanthane. Cette nouvelle structure permet d’envisager la fabrication de couches plus fines d’une épaisseur de 0,5 nm, compatibles avec les procédés en 16 nm.

Des chercheurs chinois ont réussi à fabriquer une couche isolante d’une épaisseur de 0,65 nm en utilisant un couple nitrure de hafnium/dioxyde de hafnium et en procédant à une nitruration de la surface avec de l’ammoniac avant le dépôt de la couche d’oxyde et un recuit à haute température.

Défis lithographiques à venir

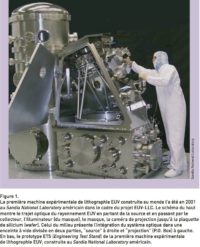

L’arrivée nécessaire de l’EUV

Le double motif continue d’être sur le devant de la scène et fut privilégié par les fondeurs, car il nécessite des temps de développement plus courts que les ultraviolets extrêmes. Ainsi, la première puce de SRAM fabriquée en 22 nm grâce au double motif est sortie des laboratoires six mois plus tôt que celle utilisant l’EUV. Néanmoins, cette méthode coûte cher et il est indéniable que le 193 nm commence à être un facteur limitatif.

La lithographie par ultraviolet extrême (EUV) est donc annoncée comme le remplaçant du laser à fluorure d’argon. Utilisant une longueur d’onde de 13,5 nm, TSMC devrait recevoir les premiers scanners en 2011 (cf. « La lithographie EUV chez TSMC en 2011 »), en même temps que Samsung, Intel et Toshiba. Cette technologie marque aussi la fin des lentilles réfractive au profit de miroirs en raison du niveau d’absorption trop important des optiques qui sont donc incompatibles avec les nouvelles longueurs d’onde.

Les laboratoires d’Intel ont aussi montré qu’ils pouvaient graver en 15 nm en utilisant le laser à exciplexe classique de 193 nm et pensent même pouvoir descendre jusqu’en 11 nm. Le problème est que les modifications nécessaires pour y arriver coûtent cher, les scanners EUV devenant alors attrayants.

De l’ingéniosité de l’homme

De l’ingéniosité de l’homme

Ces recherches répondent donc en partie aux craintes de l’ITRS qui explique que « depuis 2001, nous avons atteint un stade où l’horizon de la Roadmap défi même les projections les plus optimistes (…) Il est difficile pour la plupart des acteurs de l’industrie du semiconducteur d’imaginer comment on peut maintenir les tendances historiques d’accroissement des équipements et des coûts pendant encore quinze ans ». Il est intéressant de noter que l’ITRS elle-même, en 2006, avait du mal à envisager que l’on puisse graver en 16 nm et ce genre de discours alarmiste est monnaie courante lorsque l’on se penche sur l’histoire des transistors.

En 1983, durant le très sérieux International Electron Devices Meeting (IEDM), le professeur James Meindl, médaillé par l’IEEE pour ses travaux en microélectroniques, a clairement expliqué que l’architecture des transistors serait limitée entre le 200 nm et le 400 nm. Un an plus tard, George Heilmeier, l’un des pionniers des écrans LCD, écrivait que les circuits intégrés satureraient entre 0,3 et 0,5 micron. Ces hommes exceptionnellement brillants ne faisaient que constater les limites technologiques qui se présentaient à eux, mais les fondeurs et fabricants ont tellement voulu maintenir les objectifs dessinés par les conjectures de Moore, qu’ils ont trouvé des solutions répondant aux impossibilités physiques apparentes.

Pour prendre un exemple plus proche de nous, depuis que l’on grave en 180 nm et que la longueur du canal est descendue en dessous de 100 nm, les scientifiques peinent à concevoir des semiconducteurs plus petits. Cette finesse de gravure a marqué l’introduction de nouveaux procédés lithographiques utilisant un laser d’une longueur d’onde de 193 nm. Encore en vigueur aujourd’hui, ce type de photolithographie nous a emmenés bien plus loin que ce que les scientifiques pensaient au départ, puisqu’ils affirmaient à l’époque que cette méthode de fabrication serait remplacée par la lithographie à ultraviolet extrême lors de l’introduction du 65 nm. Or, le 193 nm reste pour l’instant maître des usines.

Il convient donc de prendre du recul par rapport aux nouveaux défis qui se posent à nous. Il est clair qu’à moins de trouver des solutions pratiques, les fondeurs buteront sur des limites qui empêcheront de continuer à utiliser des finesses plus importantes, mais il ne faut pas sous-estimer l’ingéniosité des chercheurs et les profits qui motivent les compagnies.

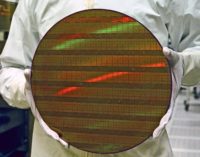

Diamètre et rendement des wafers

De l’importance du rendement

Le coût d’un die est égal au coût d’un wafer divisé par le nombre de die net par wafer. Les fondeurs estiment que le coût d’un wafer équivaut au prix de la galette, mais aussi aux frais liés à la dépréciation des équipements, l’opération de l’usine, la main-d’oeuvre, l’achat de matériaux et aux processus de fabrication. Il faut aussi savoir que le coût d’un die est différent du coût d’une puce qui inclut, entre autres, les frais engendrés lors du packaging et des différents tests jugeant de la fiabilité des circuits. Le nombre brut de die par wafer (DPW) dépend du diamètre de la galette (d en millimètre) et de la surface d’un die (S en millimètre carré) tel que

Il faut néanmoins souligner que ce chiffre ne représente pas le nombre net de puces, certains dies étant inopérants en raison d’impuretés ou défauts de fabrication. De plus, les fondeurs se réservent toujours une section de la galette à des fins de tests et contrôle de qualité. C’est pour cela que l’on parle plus souvent de rendement (le terme anglais yield est aussi couramment utilisé) que du nombre de puces réalisables sur un wafer. Le rendement est le pourcentage de puces utilisables par rapport au nombre brut de puces gravées sur un wafer. Il n’y a donc jamais un yield de 100 %. 90 % pour des architectures complexes est atteignable un an après la livraison des premières puces. Une moyenne de 70 % lors de la fabrication des premières unités est considérée comme excellente et il arrive souvent que certaines familles de puces démarrent à 50 %.

De l’importance du diamètre

De l’importance du diamètre

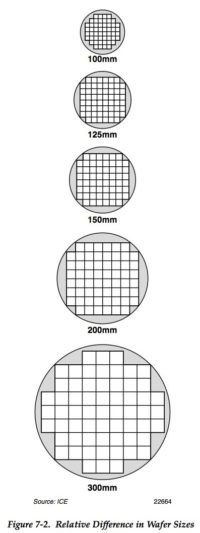

Comme on peut le voir sur la formule calculant le nombre brut de dies réalisables sur un wafer, le diamètre de la galette est l’un des éléments qui influent le plus directement les capacités de production. Cela explique pourquoi nous sommes passés de wafers de 50 mm (2 pouces) au milieu des années 1970 à des surfaces de 100 mm (4 pouces) au début des années 75, 150 mm (6 pouces) à la fin des années 80, 200 mm (8 pouces) au début des années 90 et 300 mm (12 pouces aussi nommés pizza-pie) en 2001.

Ces dates approximatives ne donnent pas le moment exact de la première utilisation desdites dimensions, mais permettent de voir que les fondeurs attendent entre 5 et 10 ans avant de passer à un modèle plus grand. Le passage du 200 mm au 300 mm fut l’un des plus longs. Comparativement, il fallut seulement 3 ans pour graver les premiers 100 millions de pouces carrés sur des wafers en 200 mm, contre 5 ans pour le 300 mm et le 450 mm (18 pouces) devrait demander encore plus de temps.

La taille d’un wafer n’est pas choisie par hasard, mais correspond au produit de l’ancien diamètre multiplié par 1,33 ou 1,5, ce qui offre une surface utilisable environ 1,8 fois ou 2,3 fois plus importante respectivement.

Défis économiques du 450 mm

Les bénéfices surpassent les coûts

Les considérations économiques sont donc le principal argument ralentissant le passage à un wafer plus grand, car en plus des usines plus de deux fois plus chères, la transition technologique peut s’avérer douloureuse. On se souvient que le bond du 200 mm (8 pouces) vers le 300 mm (12 pouces) fut particulièrement difficile avec des machines mal calibrées, des yields extrêmement faibles et beaucoup d’argent perdu. Le wafer passant rarement entre des mains humaines, il est extrêmement important de disposer de machines correctement configurées, ce qui est loin d’être facile. Les plus optimistes estiment que les fondeurs ont tiré les enseignements de cette époque et que le passage au 450 mm (18 pouces) sera beaucoup plus simple, mais tout le monde n’en est pas convaincu.

L’augmentation de la taille d’un wafer entraine aussi une augmentation importante du coût d’un wafer variant entre 70 % lors de l’introduction de la nouvelle galette sur les chaînes de production à 30 % une fois que les procédés de fabrication ont mûri. Malgré cela, un wafer plus grand apporte une réduction du coût de production du die pouvant aller de 10 % à 50 %, en raison de l’augmentation de la surface disponible. Concrètement, selon les dernières estimations, le centimètre carré sur un wafer de 450 mm coûtera 26 % moins cher à Intel que sur un 300 mm, dès les premières années de production, et Samsung parle de 29 % d’économie pour ses mémoires Flash. Ces pourcentages, similaires à ceux observés lors de l’introduction du 300 mm, augmenteront au fil du temps. Dans tous les cas, l’industrie utilise toujours deux, voire trois tailles de wafers en même temps, toutes les usines ne migrant pas au même moment. On estime qu’une galette a une durée de vie moyenne de 24 ans.

La demande est le moteur du passage au 450 mm

La demande est le moteur du passage au 450 mm

La demande toujours plus importante en NAND et DRAM et le fait que les fondeurs aient maximisé les rendements et obtiennent aujourd’hui des yields de 90 % plus facilement obligent les acteurs à considérer le 450 mm. En effet, il est plus difficile de satisfaire la demande, le 300 mm commençant à montrer ses limites et une galette plus grande est le seul moyen d’accroître sa production et fabriquer plus rapidement afin de baisser les prix, le passage à une nouvelle finesse de gravure n’étant pas suffisant pour répondre aux exigences du marché.

Si l’arrivée du 450 nm devait avoir lieu plus tard que prévue puisque l’on parle maintenant de 2015 au lieu de 2012 auparavant, les divisions entre les deux camps s’estompent, surtout depuis que les prix des usines 300 mm augmentent, rendant les bâtiments 450 mm plus attrayants.

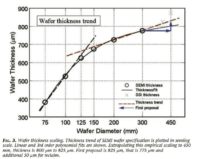

Défis industriels du 450 mm

Affaissement gravitationnel

L’épaisseur est une donnée très importante, car elle va affecter la structure de la galette. Un wafer de 300 mm pèse 128 g et on s’attend à ce qu’un modèle 450 mm tourne autour de 335 g. Or, plus un wafer est lourd et plus l’affaissement gravitationnel (le fait que le wafer plie sous l’effet de son propre poids) a des conséquences importantes sur son intégrité. Un wafer de 450 mm d’une épaisseur de 0,925 mm aura un affaissement autour de 0,350 mm. C’est plus que pour le 300 mm qui tournait à 0,100 mm. Pour combler ce défaut, il faudrait augmenter l’épaisseur du wafer afin de solidifier sa structure, mais cela coûterait trop et comporterait d’autres problèmes physiques. Les équipementiers devront donc innover pour s’assurer que les wafers restent utilisables. De plus, un modèle plus grand est aussi plus sensible aux vibrations lors de son transport.

Grands wafers, grands problèmes

Grands wafers, grands problèmes

L’augmentation du diamètre comporte aussi d’autres défis. En schématisant, la fabrication d’une galette demande du sable extrêmement propre et d’une structure atomique spécifique (le sable provient souvent des côtes australiennes) que l’on va traiter chimiquement pour le purifier à 99,999 % et obtenir un quartz (SiO2) qui est placé dans un creuset que l’on va chauffer à plus de 1 600 °C (température légèrement supérieure au point de fusion du silicium, mais en dessous de son point d’ébullition). Au bout d’une tige, on place une graine cristal de silicium qui est la plus petite forme complète du cristal et qui mesure entre 1 mm et 3 mm. On plonge la graine dans le bain, ce qui va entamer un processus de cristallisation. On retire alors la tige petit à petit pour obtenir une barre de silicium monocristalline (il s’agit d’un gros cristal et non d’un ensemble de cristaux). Ce procédé explique, en grande partie, pourquoi le wafer a une forme cylindrique. Une vidéo intéressante publiée sur YouTube décrit le phénomène mentionné.

Un changement de discours

Nous avons néanmoins assisté à un changement de mentalité des détracteurs du 450 mm ces dernières années. On se souvient qu’en 2006, de nombreux fondeurs et équipementiers, plus petits que les Samsung, Intel ou TSMC, clamaient que l’on resterait éternellement en 300 mm. Aujourd’hui, la demande les a motivés à travailler sur des éléments de réponses et l’utilisation de wafers de 450 mm dans cinq à sept ans semble devenir une réalité.