Petit bilan du Flash Memory Summit pour la marque.

Lors de la Flash Memory Summit, Toshiba a été la star du salon. En plus de son nouveau facteur de forme XFMExpress qui a remporté le prix Best of Show, l’entreprise a également présenté plusieurs produits, dont le SSD NVMe PCIe Gen4 Toshiba CM6. La firme a donné des détails sur sa mémoire ultra-rapide XL-Flash, des informations sur les prochaines générations de sa mémoire BiCS et aussi sur le développement du PLC.

PLC et XL-Flash

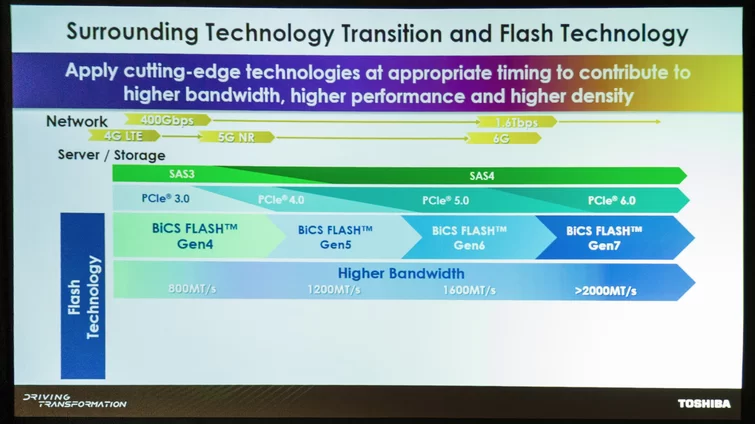

En ce qui concerne la mémoire BiCS, chaque nouvelle génération coïncidera avec celles de la norme PCIe. Ainsi, Toshiba commercialisera prochainement la BiCS-5 en PCIe 4.0. Suivront la BiCS-6 et la BiCS-7. La société n’a pas donné de calendrier précis. On sait simplement que la BiCS-5 offrira une bande passante de 1200 T/s, que la BiCS-6 atteindra 1600 T/s et la BiCS-7 2000 T/s.

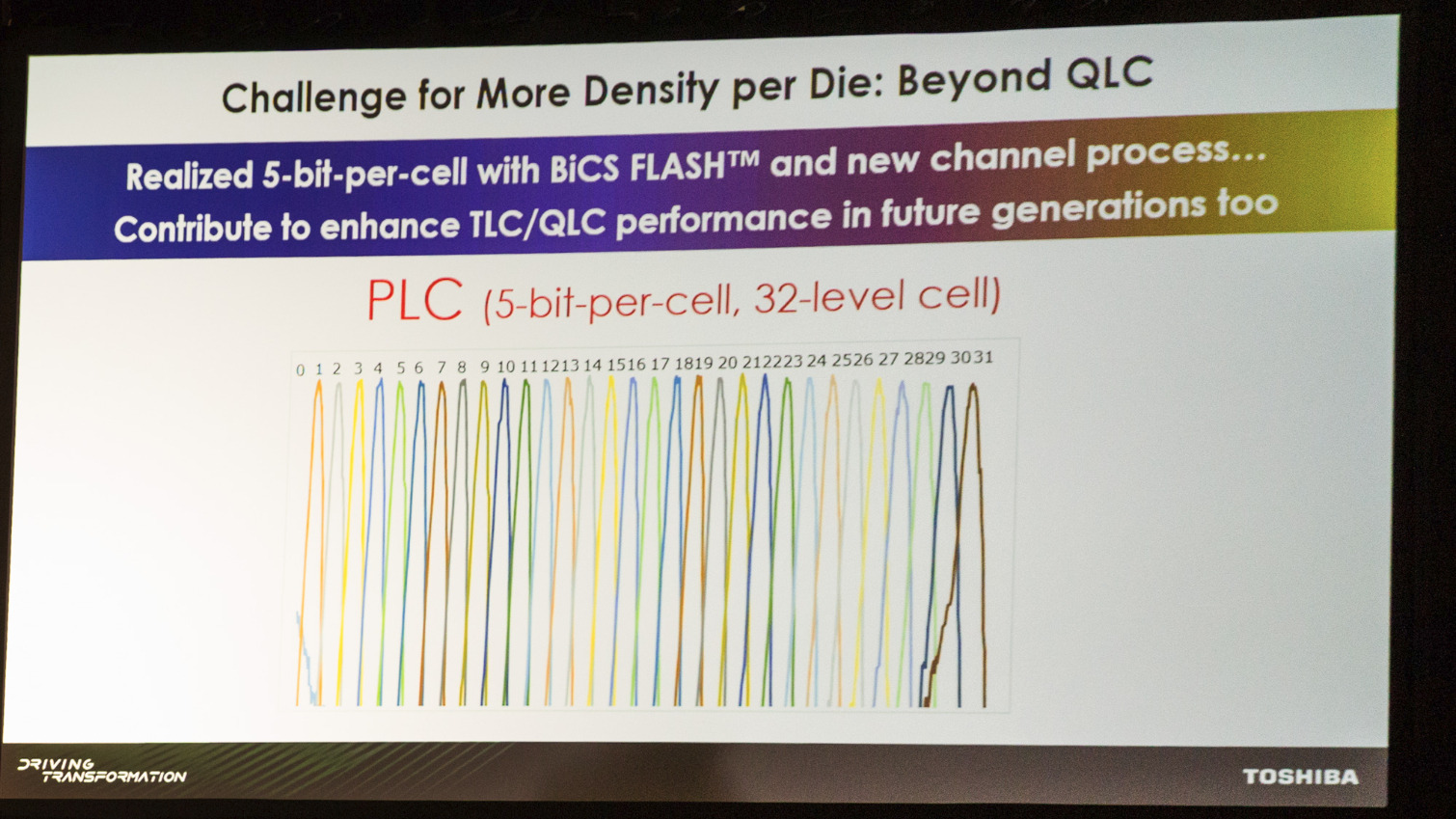

Toshiba a également indiqué avoir débuté les recherches sur le successeur du QLC, la mémoire flash NAND à cinq bits par cellule (PLC). Celle-ci stocke jusqu’à 32 niveaux de tension distincts, que les contrôleurs SSD doivent gérer avec précision. Et si le QLC est déjà assez lent et a une endurance plus faible que les autres types de flash, le PCL accentuera ces défauts. Cependant, le débit et la latence bénéficieront des nouvelles caractéristiques du protocole NVMe, telles que les Zoned Namespaces (ZNS). Cette technologie réduit l’amplification de l’écriture, le besoin de sur approvisionnement et l’utilisation de la DRAM par le contrôleur interne.

Enfin, parmi les autres annonces importantes, il y avait bien sûr la mémoire XL-Flash, la réponse de Toshiba à la mémoire Z-NAND de Samsung et Optane d’Intel. Les premières pièces s’armeront d’un die de 128 Gb (en boîtiers de 2, 4 ou 8 puces) en 16 couches. Selon Toshiba, la latence en lecture est inférieure à 5 microsecondes. La production en série doit débuter l’année prochaine.