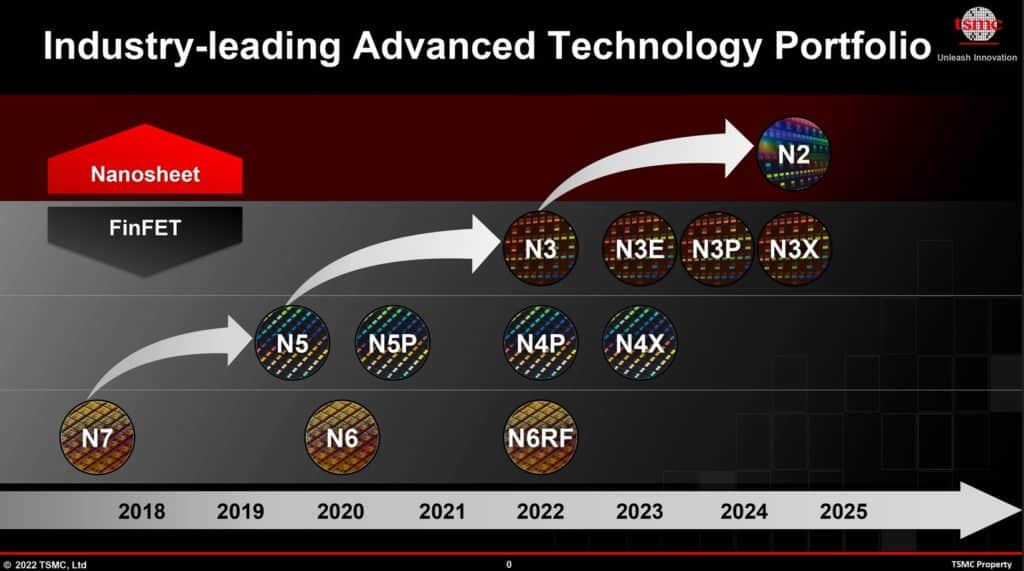

N3, N3E, N3P, N3X et N2 ; mais également FinFlex, une fonctionnalité visant à améliorer la flexibilité de conception.

Hier, TSMC a détaillé ses procédés de fabrication N3 (3 nm) et N2 (2 nm). Pour le N3, le fondeur met en avant sa stratégie FinFlex. Celle-ci offre aux concepteurs de puces plus de flexibilité afin qu’ils puissent plus facilement optimiser les performances, la puissance et la taille de leurs produits. Le 2 nm marquera la transition vers une toute nouvelle plateforme technologique synonyme de transistors nanosheet (GAAFET).

Le principe des transistors GAAFET consiste en des canaux entourés de grilles afin de réduire les fuites. Ces canaux peuvent être élargis pour augmenter la puissance et améliorer les performances ou, au contraire, rétrécis pour minimiser la consommation d’énergie. L’alimentation s’effectue par le biais d’un système baptisé BEOL (back-end-of-line).

Apple et Intel, premiers à adopter la gravure en 2 nm de TSMC

N3

La classe 3 nm englobe cinq nœuds en tout. Le nœud principal est le N3 dont la production en volume doit débuter dans le courant de l’année. Les N3E et N3P amélioreront le ratio performance / watt. Le N3S offrira une meilleure densité de transistors tandis que le N3X autorisera des tensions plus élevées. Tous ces nœuds de gravure mènent à 2024 voire 2025 pour le dernier.

| Nœuds | N3 vs N5 | N3E vs N5 |

| Augmentation fréquence à puissance identique | +10 % ~ 15 % | +18 % |

| Réduction consommation à fréquence identique | -25 % ~ -30 % | -34 % |

| Augmentation densité logique | 1,6x | 1,7x |

| Début production de masse | S2 2022 | T2/T3 2023 |

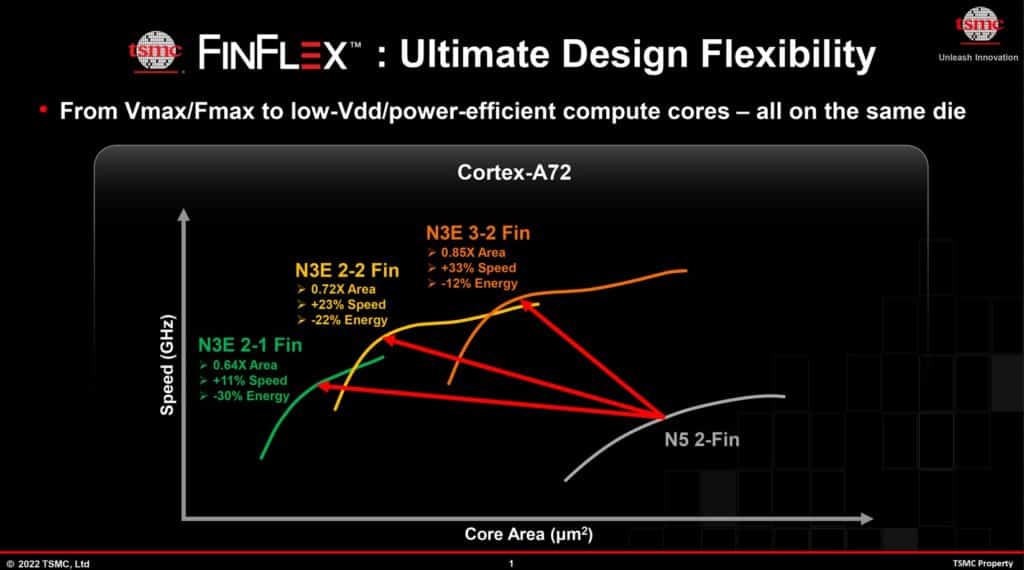

Par ailleurs, la fonctionnalité FinFlex vise à accroître la flexibilité en accordant aux concepteurs de puces plus de choix pour chaque bloc ; c’est une sorte de boîte à outils à transistors en quelque sorte. Les transistors FinFET 2-1 garantissent une surface réduite et une faible consommation d’énergie. À l’inverse, les FinFET 3-2 maximisent les performances au détriment de la surface et de la consommation. Bien sûr, ces différentes configurations FinFET s’ajoutent aux bibliothèques de blocs logiques pour une multitude de configurations.

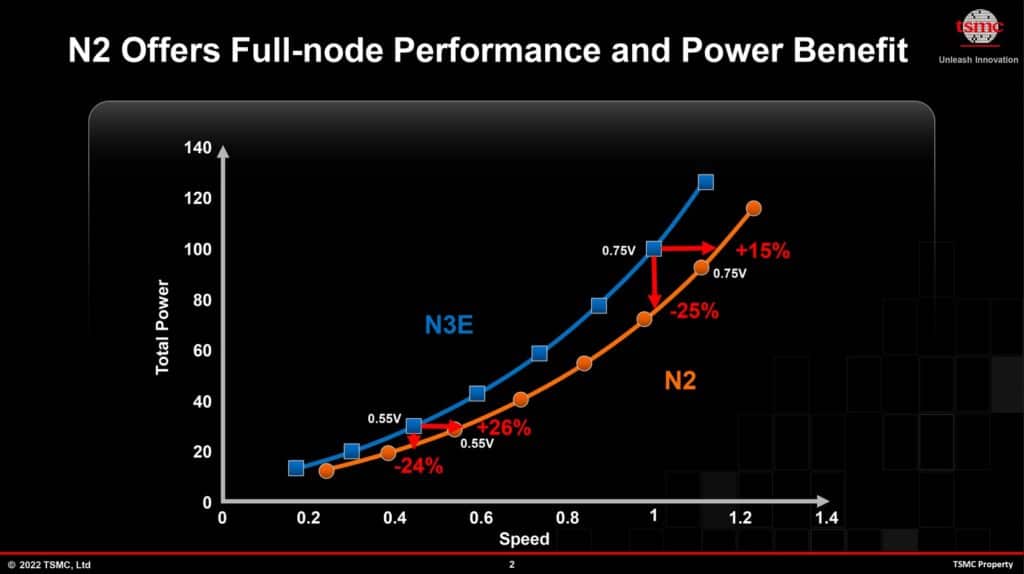

N2

TSMC prévoit de graver en 2 nm à partir de 2025. Par rapport au N3E, le N2 doit délivrer des fréquences de 10 à 15 % supérieures à puissance et complexité égales ; une consommation d’énergie inférieure de 25 à 30 % à fréquence et nombre de transistors identiques. La densité n’augmentera en revanche que de 10 %.

| Nœuds | N5 vs N7 | N3 vs N5 | N3E vs N5 | N2 vs N3E |

| Augmentation fréquence à puissance identique | +15 % | +10 % ~ 15 % | +18 % | +10 % ~ 15 % |

| Réduction consommation à fréquence identique | -30 % | -25 % ~ 30 % | -34 % | -23 % ~ -30 % |

| Augmentation densité logique | ? | ? | 1,3X | >1,1X |

| Début production de masse | T2 2022 | S2 2022 | T2/T3 2023 | S2 2025 |

Sources : TSMC, Tom’s Hardware US