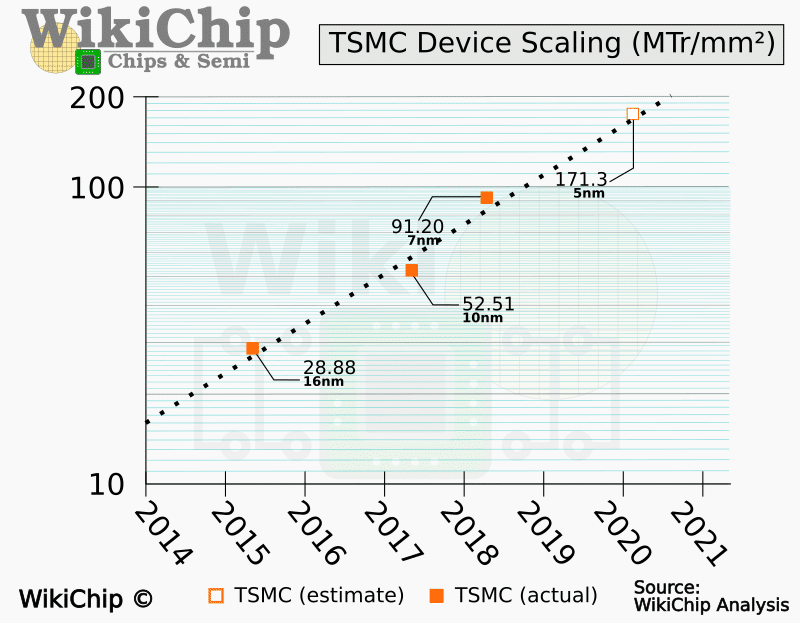

Une densité de 171,3 millions de transistors par mm².

En début de mois, on a appris que TSMC lançait la production de masse en 5 nm dès avril, avec le N5. Dans les semaines qui suivront, l’entreprise proposera un nœud N5P, une version optimisée du N5. Par rapport au N7 (7 nm DUV), ce process augmente la densité des transistors de 84 %.

C’est en tout cas le chiffre avancé par WikiChip. Le N5P permet une densité de 171,3 millions de transistors par mm². Le N7 se limite à 91,2 millions de transistors par mm².

NVIDIA sera l’un des principaux clients de la plateforme CoWoS de TSMC

Pour les puces A14 d’Apple

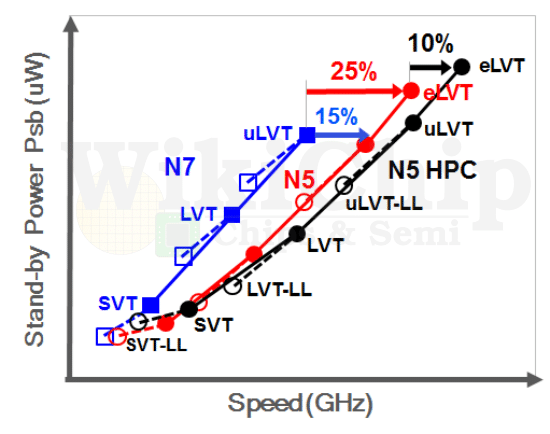

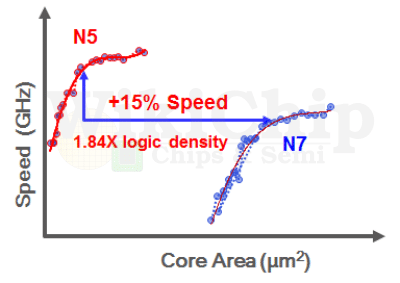

Comme on l’avait vu précédemment, ce N5P s’annonce entièrement IP compatible avec le processus N5 EUV. Il offre une réduction de la surface de puce de 35 à 40 % par rapport au N7. De plus, il augmente les fréquences de 15 % à consommation égale ou réduit la consommation d’énergie de 30 % à fréquences équivalentes. Enfin, notez que c’est Apple qui sera le plus gros client de TSMC cette année pour le 5 nm, avec son SoC A14.