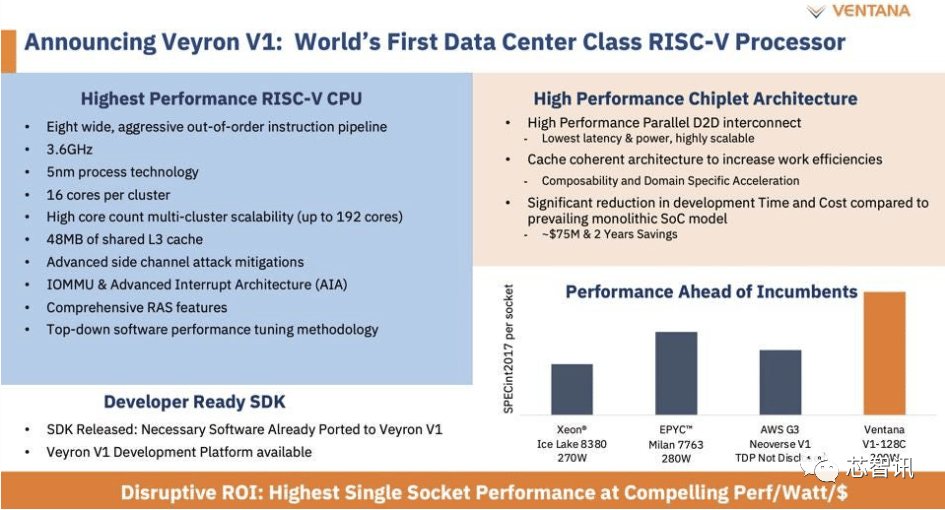

Avec cette puce, conçue en 5 nm, la société ambitionne de concurrencer les processeurs x86 Intel Xeon et AMD EPYC sur un secteur ou même Arm a du mal à le faire, celui des serveurs.

À l’occasion du RISC-V Summit, qui se déroule à San Jose, la startup Ventana Microsystems, spécialisée dans la conception de processeurs RISC-V, a présenté le premier sous cette architecture destiné aux serveurs, le Veyron V1. Ce n’est bien sûr pas un secteur sur lequel on s’attend à voir des puces RISC-V. Jusqu’à présent, cette architecture de jeu d’instructions open source, sert surtout pour le marché de l’Internet des objets et autres systèmes embarqués.

À l’instar des cœurs de processeur P670 et P470 dévoilés par SiFive début novembre, cette puce Veyron V1 est élaborée sur le processus de gravure 5 nm. Chaque cluster renferme 16 cœurs, et la capacité totale par puce est de 192 cœurs. Le cache L3 partagé est de 48 Mo. Concernant la fréquence, elle s’élève jusqu’à 3,6 GHz selon Ventana Microsystems. L’entreprise met également en avant une sécurité avancée grâce à des mesures d’atténuation d’attaques par canaux auxiliaires, le recours aux technologies IOMMU (input–output memory management unit) et AIA (advanced interrupt architecture) et des fonctionnalités RAS (reliability, availability and serviceability ; “un terme d’ingénierie du matériel informatique impliquant l’ingénierie de la fiabilité, la haute disponibilité et la conception de la facilité d’entretien”).

Pour son HPSC, la NASA a choisi des cœurs CPU RISC-V SiFive

Bientôt une bataille à 4 ?

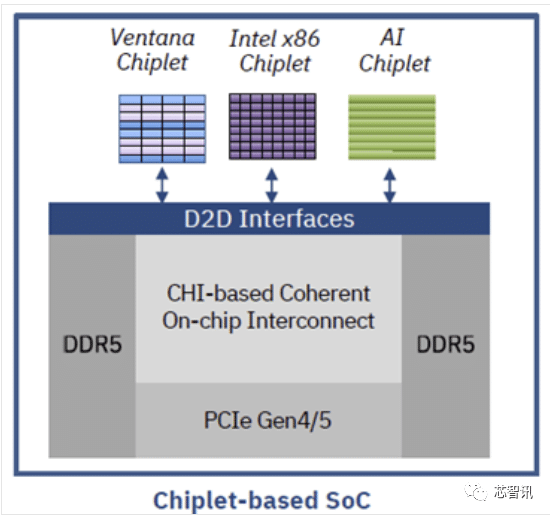

Par ailleurs, la conception générale de la puce est assez classique : une interface de données D2D sur un côté, de la mémoire DDR5 sur deux autres et du PCIe Gen5 sur le dernier. L’interface Die-to-Die (D2D) est compatible Harness of Wire (HoW) et Universal Chiplet Interconnect Express (UCIe), des protocoles également pris en charge par Intel, AMD, NVIDIA ou Arm.

Comme indiqué en début d’article, pour le moment, l’architecture RISC-V est principalement utilisée sur le marché de l’informatique embarquée. Plusieurs raisons à cela : sa capacité à offrir une utilisation efficace de l’énergie, sa viabilité à long terme, ou simplement le fait que l’architecture soit ouverte et libre. L’avenir nous dira si le Veyron V1 parvient à se faire une place au sein des serveurs, terrain de jeu des processeurs x86 Xeon d’Intel et EPYC d’AMD, sur lequel commence toutefois à légèrement empiéter les puces Arm.

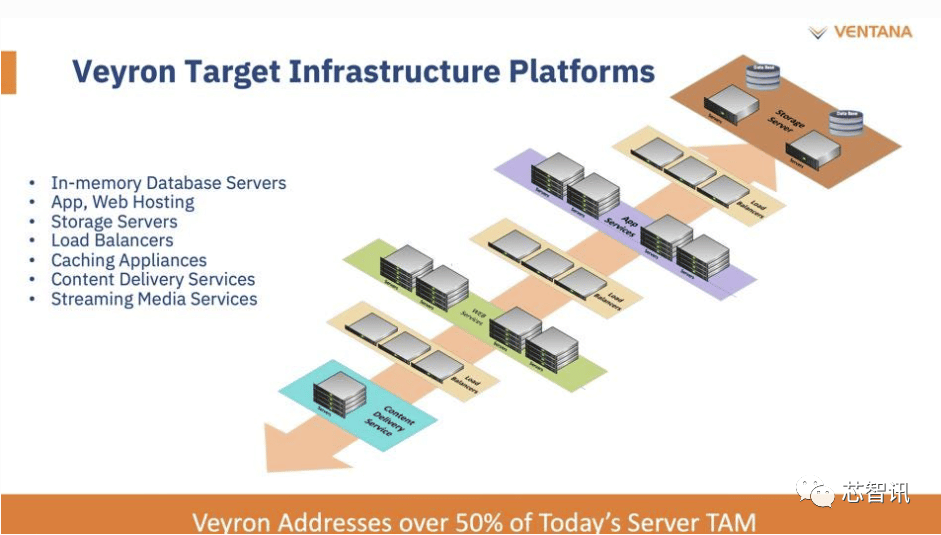

Ventana Microsystems suggère que sa V1 peut servir à de nombreuses tâches, des hébergeurs web aux centres de données consacrés aux services de streaming.

Source : Mydrivers