L’avenir est à l’empilement 3D.

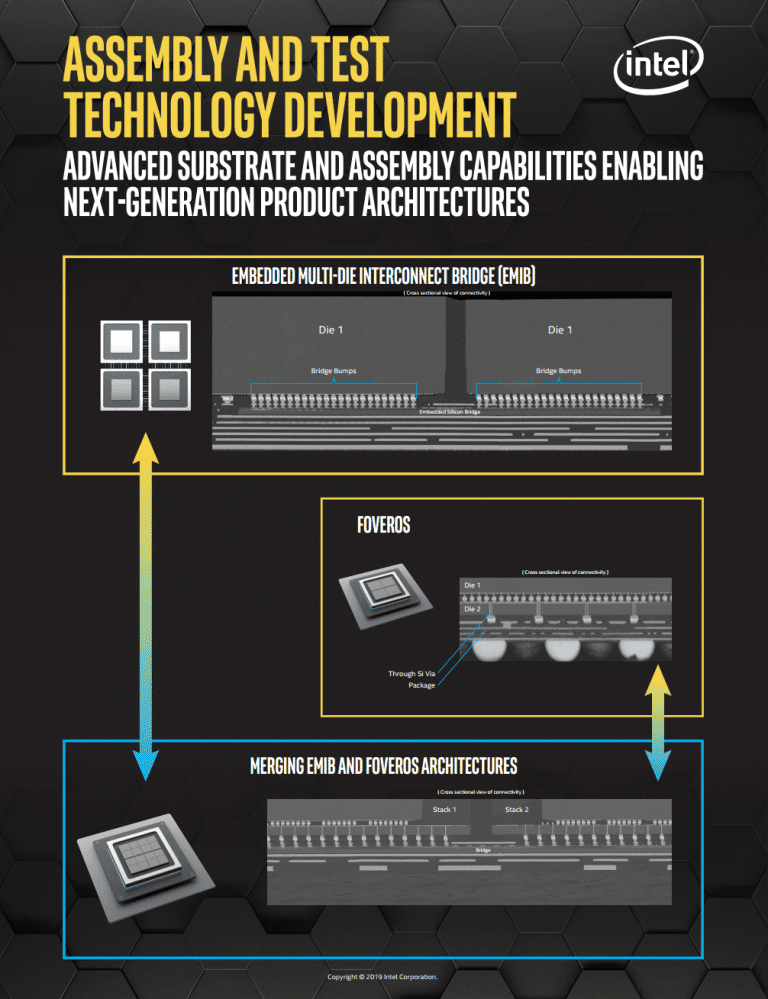

Lors de la Semicon qui se déroule actuellement à San Francisco, Intel a présenté les mises à jour apportées sur ses technologies EMIB et Foveros. Pour rappel, Forevos permet l’empilement 3D. L’EMIB (Embedded Multi-Die Interconnect Bridge) est une couche d’interconnexion qui relie les dies d’un même package entre eux. L’entreprise a également présenté une nouvelle technologie ODI (Omni-Directional Interconnect).

| À lire aussi : AMD : des processeurs empilés refroidis grâce à l’effet Peltier ? |

Des TSV plus larges

Cette nouvelle interconnexion omnidirectionnelle offre plus de flexibilité pour la communication entre les puces d’un même package. La communication horizontale fonctionne comme dans l’EMIB. Mais les échanges se font aussi verticalement grâce au TSV (Through Silicon Via). Cette ODI utilise de larges vias verticaux pour permettre l’alimentation des parties supérieures directement depuis la base du substrat. Beaucoup plus larges que dans les TSV traditionnels, ces grands vias offrent une résistance plus faible, plus de bande passante, tout en étant plus robustes. Par conséquent, leur nombre est moindre. Ainsi, cela autorise une meilleure optimisation et libère plus d’espace pour les transistors.

Intel a également présenté une nouvelle interface die-to-die MDIO (Management Data Input/Output). En plus d’une meilleure efficacité énergétique, elle double la vitesse des broches et la densité de bande passant par rapport à l’AIB (Advanced Interface Bus).

Babak Sabi, vice-président du développement chez Intel, a déclaré : “Notre vision est de développer une technologie de pointe pour connecter les puces et les chiplets dans un ensemble qui correspond à la fonctionnalité d’un système monolithique sur puce. Une approche hétérogène donne à nos architectes une flexibilité sans précédent pour mélanger et faire correspondre des blocs IP et des technologies de traitement avec divers éléments de mémoire et d’E/S dans des dispositifs avec de nouveaux facteurs de forme. La structure verticalement intégrée d’Intel offre un avantage à l’ère de l’intégration hétérogène. Elle nous permet une co-optimisation de l’architecture, des processus et du packaging pour fournir des produits de premier plan”.

C’est pas mal du tout, mais reste la mise en place reelle et surtout le cout.

Et j’espere qu’Intel va un peu voir aussi a la securité dans ses processeur et se remettre en question.